Sundance SMT702 User Manual

Page 46

0

TOC[13:0]

Default

‘00000000’

Offset 0x0400 -

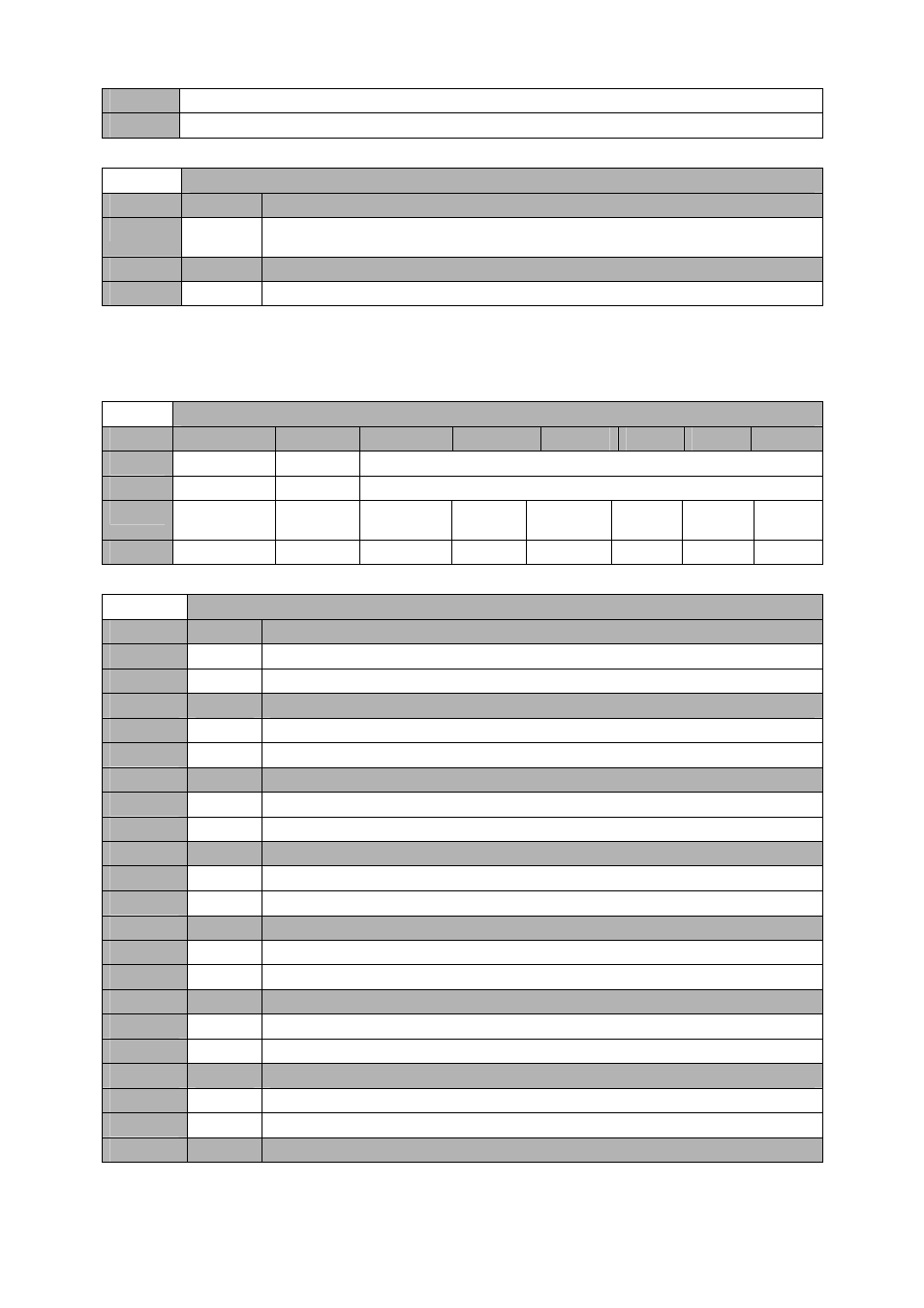

Frequency Synthesizer (LMX2531) Register R4 – 0xD0 (write and read)

Setting

Bit 13-0

Timeout Counter for fastlock (TOC[13:0])

0

0

0x0 Timeout 0 – 0x1 Timeout always enable – 0x2 – timeout 0 – 0x3 timeout 0 – 0x4

timeout 4x2 phase detector - … - 0x3FFF 16383x2 phase detector

Setting

Bit 17-14

Charge Pump Current for fastlock ICPFL[3:0]

0

0

0x0 corresponds to 90uA (state 1x) and 0xF (State 16x) to 1440uA (90uA per state)

4.3.1.2.23

Frequency Synthesizer (LMX2531) Register R5 – 0xD4

(write and read).

Offset 0x0400 -

Frequency Synthesizer (LMX2531) Register R5 – 0xD4 (write and read)

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

TOC[13:0]

Default

‘000000’

0

Reserved

EN_DIGLO

D

EN_PLLLDO

2

EN_PLLL

DO1

EN_VCOLD

EN_OSC

EN_VCO

EN_PLL

Default

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

Offset 0x0400 -

Frequency Synthesizer (LMX2531) Register R5 – 0xD4 (write and read)

Setting

Bit 0

Enable bit for pll – EN_PLL

0

0

PLL powered off

1

1

PLL powered on

Setting

Bit 1

Enable bit for vco – EN_VCO

0

0

VCO powered off

1

1

VCO powered on

Setting

Bit 2

Enable bit for Oscillator inverter – EN_OSC

0

0

Reference Oscillator powered off

1

1

Reference Oscillator powered on

Setting

Bit 3

Enable bit for VCO LDO – EN_VCOLDO

0

0

LDO powered off

1

1

LDO powered on

Setting

Bit 4

Enable bit for PLL LDO1 – EN_PLLLDO1

0

0

LDO powered off

1

1

LDO powered on

Setting

Bit 5

Enable bit for PLL LDO2 – EN_PLLLDO2

0

0

LDO powered off

1

1

LDO powered on

Setting

Bit 6

Enable bit for Digital LDO – EN_DIGLDO

0

0

PLL powered off

1

1

PLL powered on

Setting

Bit 14

Reset all register REG_RST