Sundance SMT702 User Manual

Page 35

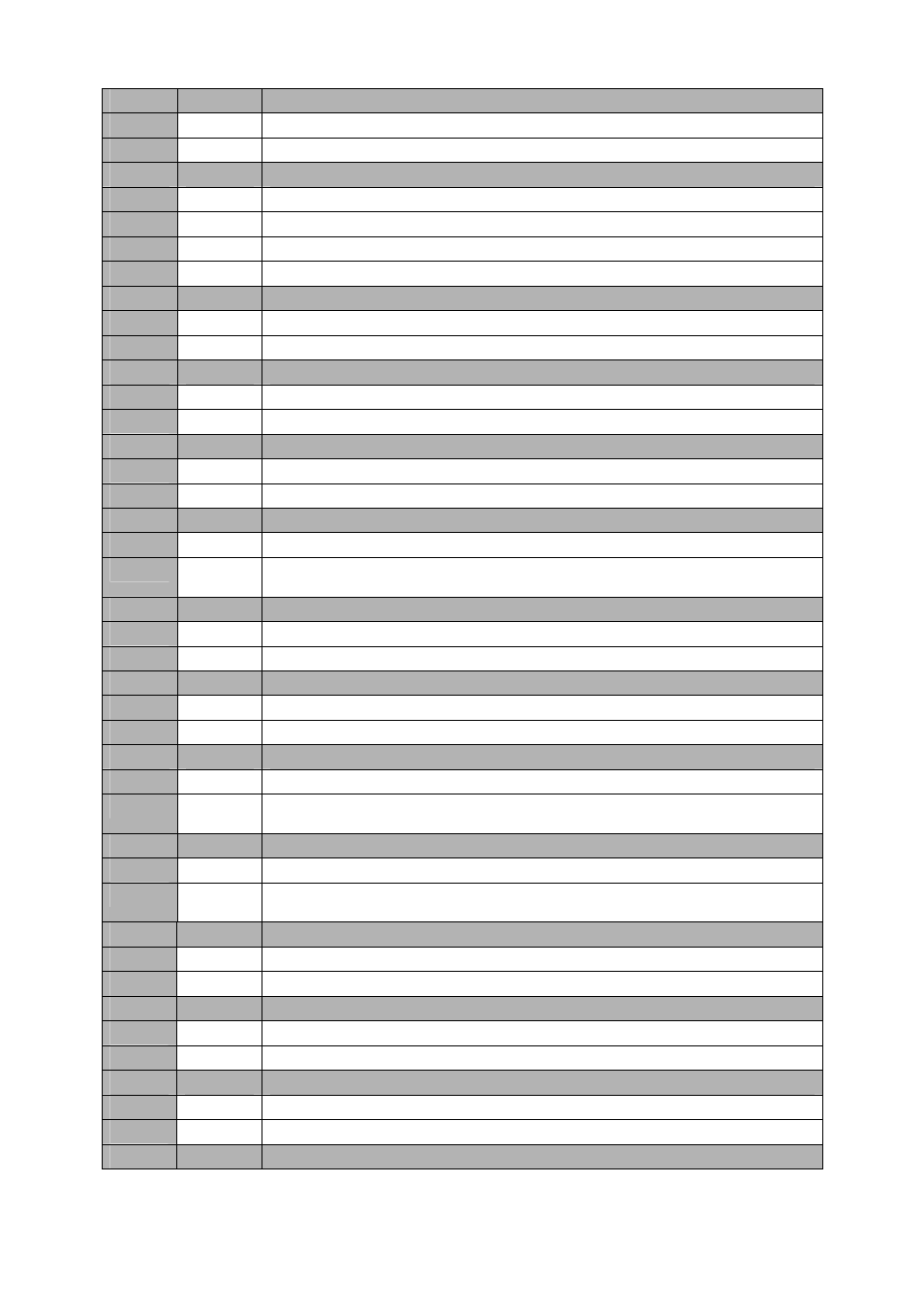

Setting

Bit 7

Description – Sampling Clock Source Selection

0

0

ADCs are clocked using the on-board clock synthesizer.

1

1

ADCs are clocked using an external source.

Setting

Bit 9-8

Description – Reference Clock Selection

0

00

External Reference Selected.

1

01

100-MHz PXI Express Reference Clock.

2

10

10-MHz PXI Express Reference Clock.

3

11

100-MHz PXI Express Reference Clock.

Setting

Bit 10

Description – Reference Clock Circuitry Reset

0

0

Normal Mode of Operation.

1

1

Reference Clock Circuitry kept in Reset (Default).

Setting

Bit 12

Description – Reference Clock Out Divider.

0

0

Divide by 1.

1

1

Divide by 2.

Setting

Bit 13

Description – On-board Reference Clock Divider

0

0

Divide by 1.

1

1

Divide by 2.

Setting

Bit 14

Description – ADCs Calibration Request (Auto-Clears)

0

0

Normal Mode of Operation (Default)

1

1

Forces the FPGA to recalibrate its IOs. This is required when the sampling clock of the

ADCs has been changed.

Setting

Bit 15

Description – ADC DCMs Reset

0

0

Normal Mode of operation

1

1

Resets ADC DCMs.

Setting

Bit 16

Description – DDR2 Capture Enable

0

0

DDR2 Memory not enabled. Nothing can be written.

1

1

DDR2 memory enabled, meaning samples can be written in memory until it is full.

Setting

Bit 17

Description – Trigger Source Selection

0

0

On-board trigger selected (bit 16)

1

1

External trigger selected (Trig Input). A Level ‘high’ on the Trig Input is required to start

an acquisition (length of the pulse being at least 1/8

th

of the ADC sampling clock.

Setting

Bit 18

Description – DDR2 read Enable

0

0

DDR2 Memory read operation not enabled.

1

1

DDR2 memory read operation enabled, meaning samples contained in DDR2 memory can

be transferred to the host.

Setting

Bit 19

Description – DDR2 Reset

0

0

Normal Mode of Operation

1

1

Keeps DDR2 circuitry in Reset

Setting

Bit 20

Description – SHB1 Reset

0

0

Normal Mode of Operation

1

1

Keeps SHB1 circuitry in Reset

Setting

Bit 21

Description – SHB2 Reset

0

0

Normal Mode of Operation

1

1

Keeps SHB2 circuitry in Reset

Setting

Bit 22

Description – Soft Reset