Sundance SMT702 User Manual

Page 39

0

0

9-bit value – With all bits set, adjust=110ps.

4.3.1.2.10

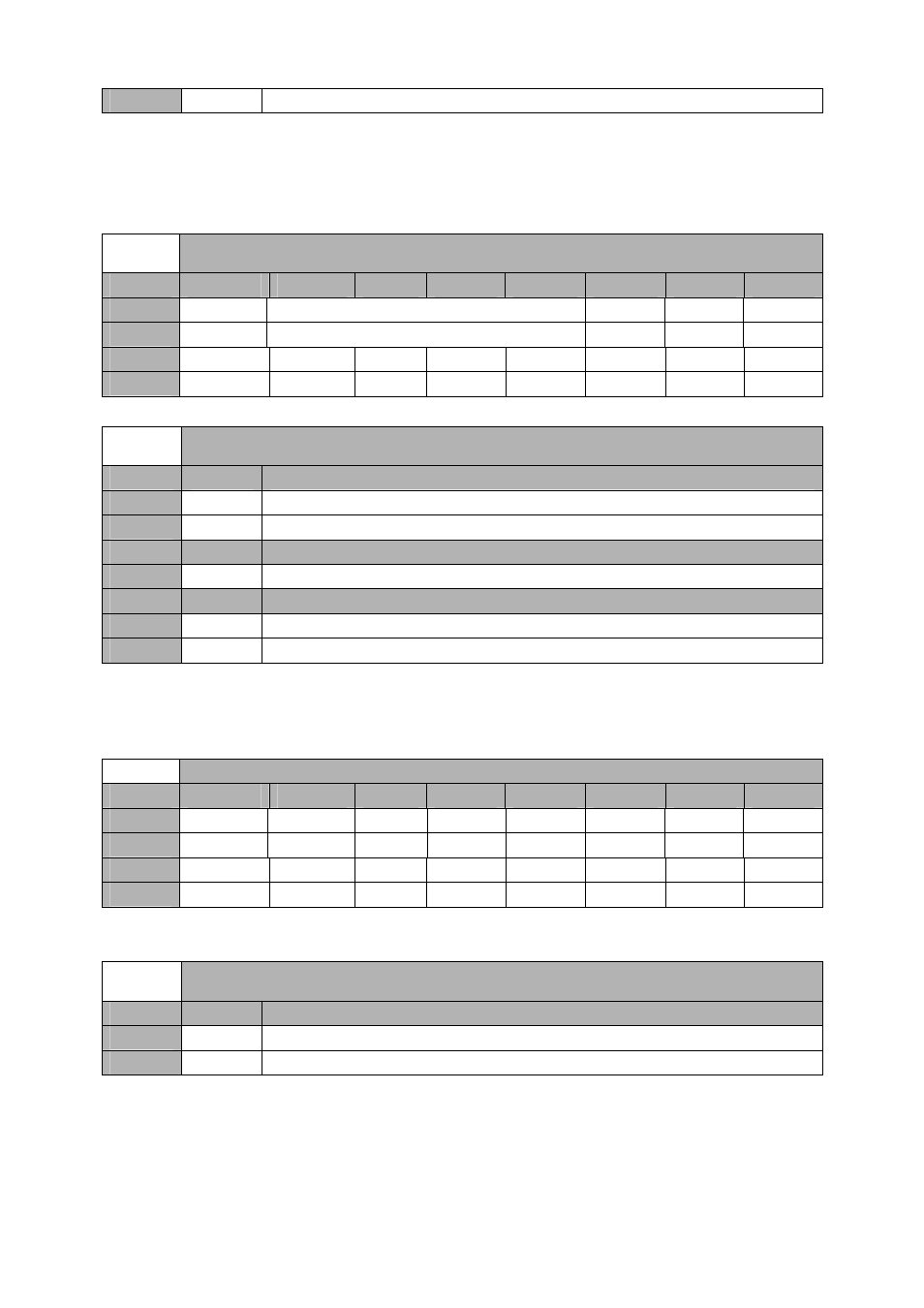

ADCA (ADC083000) Register 0xE – Extended Clock Phase

Adjust Coarse – 0x78 (write and read).

Offset 0x0400 -

ADCA (ADC083000) Register 0xE – Extended Clock Phase Adjust Coarse – 0x78

(write and read)

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

ENA

Phase Adjust (Coarse)

LFS

Reserved

Reserved

Default

‘0’

‘0’

‘1’

‘1’

0

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Default

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

Offset 0x0400 -

ADCA (ADC083000) Register 0xE – Extended Clock Phase Adjust Coarse

– 0x78 (write and read)

Setting

Bit 10

Description (LFS – Low Frequency Sample Clock)

0

0

Sample Clock above 900MHz.

1

1

Sample Clock below 900MHz.

Setting

Bit 11-14

Description (Coarse Adjust Magnitude)

0

0

4-bit value – Each LSB adds approximately 70ps of Clock Adjust.

Setting

Bit 15

Description (ENA - enable)

0

0

Disabled.

1

1

Enabled.

4.3.1.2.11

ADCA (ADC083000) Register 0xF – Test Pattern register –

0x7C (write and read).

Offset 0x0400 -

ADCA (ADC083000) Register 0xF – Test Pattern Register – 0x7C (write and read)

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

1

Reserved

Reserved

Reserved

Reserved

TPO

Reserved

Reserved

Reserved

Default

‘1’

‘1’

‘1’

‘1’

‘0’

‘1’

‘1’

‘1’

0

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Reserved

Default

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

‘1’

Offset 0x0400 -

ADCA (ADC083000) Register 0xF – Test Pattern Register – 0x7C (write

and read)

Setting

Bit 11

Description (TPO – Test Pattern Output Enable)

0

0

Normal mode of Operation.

1

1

All ADC outputs in Test Pattern mode.