2 register descriptions, 1 general control register – 0x8 (read-only) – Sundance SMT702 User Manual

Page 31

4.3.1.2

Register Descriptions

4.3.1.2.1

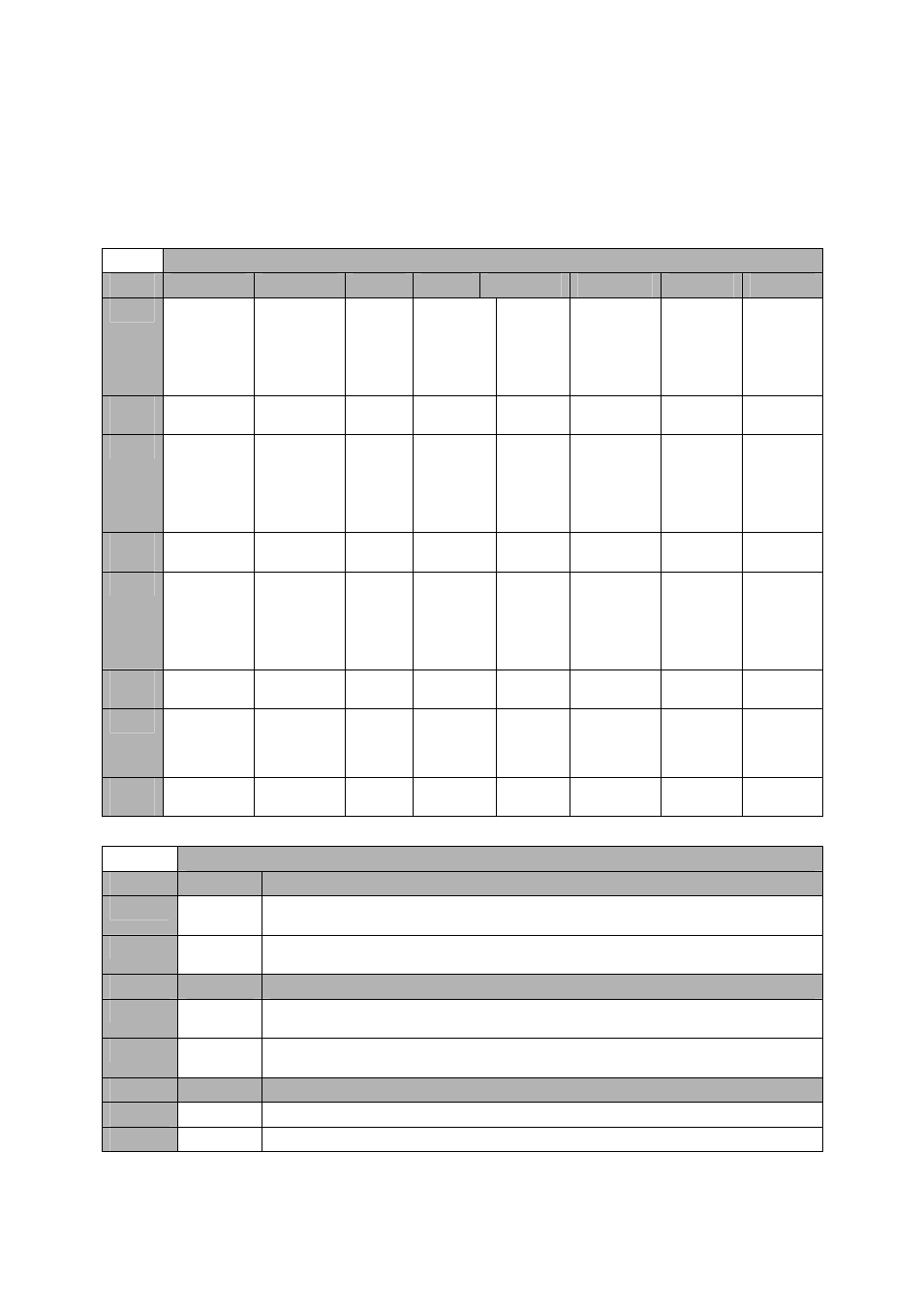

General Control Register – 0x8 (read-only).

Offset 0x0400 –

General control Register – 0x8 (Read-only register).

Byte

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

3

ADCb synch

reference

state

ADCa synch

reference

state

System

Monitor

–

Vccaux

alarm

System

Monitor –

Vccint

alarm

System

Monitor

– Die

temperat

ure

alarm

DDR2 Fifo

Almost

Empty

(Memory

Bank B)

DDR2 Fifo

Almost

Empty

(Memory

Bank A)

DDR2 Fifo

Full

(Memory

Bank B)

Defaul

t

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

2

DDR2 Fifo

Full

(Memory

Bank A)

DDR2 Fifo

Ready

(Memory

Bank B)

IDelay

Control

Ready

(Memor

y Bank

B)

DDR2 Fifo

empty

(Memory

Bank B)

DDR2

lock

status

(Memory

Bank B)

DDR2 phy

init done

(Memory

Bank B)

Ddr2 Fifo

Ready

(Memory

Bank A)

IDelay

Control

Ready

(Memory

Bank A)

Defaul

t

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘1’

‘1’

1

DDR2 Fifo

empty

(Memory

Bank A)

DDR2 lock

status

(Memory

Bank A)

DDR2

phy init

done

(Memor

y Bank

A)

ADCb

calibrati

on

complete

d

ADCa

calibration

completed

ADCa

DCM Busy

ADCb

DCM Busy

Defaul

t

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘1’

‘1’

0

ADCB

Programme

d

ADCA

Programme

d

ADCb

DCM

Lock

Status

ADCa DCM

Lock

Status

Lock

Detect

(Clock

Chip)

Clock Chip

Programme

d

ADCB

Calibratio

n Running

ADCA

Calibratio

n Running

Defaul

t

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

‘0’

Offset 0x0400 –

General control Register – 0x8 (Read-only register).

Setting

Bit 0

Description – ADCA Calibration Running

0

0

Normal Mode of Operation – ADCA not calibrating. A calibration cycle lasts 14000

sampling clock cycles.

1

1

ADCA is busy running a Calibration cycle. A calibration cycle lasts 14000 sampling clock

cycles. Nothing should be done while ADCa is in the middle of a calibration cycle.

Setting

Bit 1

Description – ADCB Calibration Running

0

0

Normal Mode of Operation – ADCB not calibrating. A calibration cycle lasts 14000

sampling clock cycles.

1

1

ADCB is busy running a Calibration cycle. A calibration cycle lasts 14000 sampling clock

cycles. Nothing should be done while ADCb is in the middle of a calibration cycle.

Setting

Bit 2

Description – Clock chip programmed

0

0

Clock chip not yet programmed.

1

1

Clock chip has been programmed with all registers after an update request has been sent.