Sundance SMT702 User Manual

Page 30

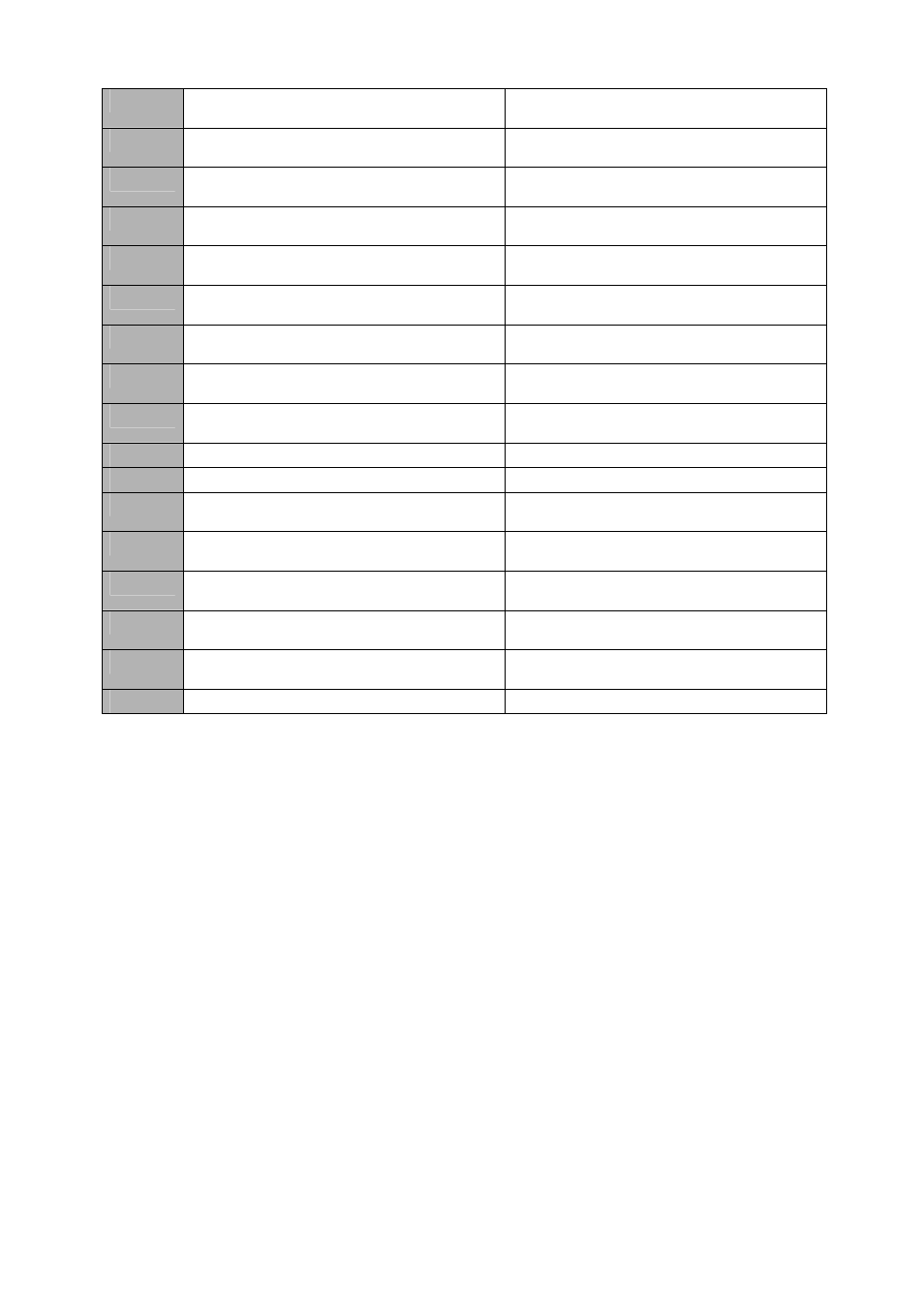

0xC8

Frequency Synthesizer (LMX2531) register R2

Read-back (FPGA register) Frequency Synthesizer

(LMX2531) register R2

0xCC

Frequency Synthesizer (LMX2531) register R3

Read-back (FPGA register) Frequency Synthesizer

(LMX2531) register R3

0xD0

Frequency Synthesizer (LMX2531) register R4

Read-back (FPGA register) Frequency Synthesizer

(LMX2531) register R4

0xD4

Frequency Synthesizer (LMX2531) register R5

Read-back (FPGA register) Frequency Synthesizer

(LMX2531) register R5

0xD8

Frequency Synthesizer (LMX2531) register R6

Read-back (FPGA register) Frequency Synthesizer

(LMX2531) register R6

0xDC

Frequency Synthesizer (LMX2531) register R7

Read-back (FPGA register) Frequency Synthesizer

(LMX2531) register R7

0xE0

Frequency Synthesizer (LMX2531) register R8

Read-back (FPGA register) Frequency Synthesizer

(LMX2531) register R8

0xE4

Frequency Synthesizer (LMX2531) register R9

Read-back (FPGA register) Frequency Synthesizer

(LMX2531) register R9

0xE8

Frequency Synthesizer (LMX2531) register R12

Read-back (FPGA register) Frequency Synthesizer

(LMX2531) register R12

0x108

ADCA – DCM Phase Shift.

Reserved.

0x10C

ADCB – DCM Phase shift.

Reserved.

0x180

FPGA Die temperature thresholds.

System Monitor – Read-back FPGA die

temperature measured

0x184

FPGA Core voltage thresholds.

System Monitor – Read-back FPGA Vccint (Core

Voltage) measured

0x188

FPGA Aux voltage thresholds

System Monitor – Read-back FPGA Vccaux (Core

Voltage) measured

0x18C

Reserved

Amount of samples left to be read out out of

DDR2 BankA

0x190

Reserved

Amount of samples left to be read out out of

DDR2 BankB

Figure 14 – Register Memory Map.

Note that ADC registers are write-only (ADC chips), which means that the contents

of the ADC registers can only be read-back from the FPGA. THe same applies to the

Clock chip.