5 status register, 6 dma, interrupt & trigger control – Measurement Computing CIO-DAS16Jr/16 User Manual

Page 18

3.5 STATUS REGISTER

BASE ADDRESS + 8

CH1

CH2

CH4

CH8

INT

MUX

U/B

EOC

0

1

2

3

4

5

6

7

A read mostly, one-function-write register.

READ

EOC = 1, the A/D converter is busy. EOC = 0, it is free.

U/B = 1, the amplifier is in Unipolar mode. U/B = 0, is bipolar.

MUX = 1, Channels are configured 16 single ended. MUX = 0, 8 differential.

INT = 1, an external pulse has been received. INT = 0, the flip-flop is ready to receive a pulse..

There is a flip-flop on the TRIGGER input (pin 25) which will latch a pulse as short as 200 nanoseconds. Once

triggered, this flip-flop must be reset by a write to this register. Your interrupts service routine must do this before

another interrupt trigger can be received.

CH8, CH4, CH2 & CH1 are a binary number between 0 and 15 indicating the channel number that the MUX is

currently set to and is valid only when EOC = 0. The channel MUX increments shortly after EOC = 1 so may be in a

state of transition when EOC = 1. The binary weight of each bit is shown in Table 3-1 above.

WRITE

A write of any data to this register resets the flip-flop on the pin 25 input and sets the INT bit to 0.

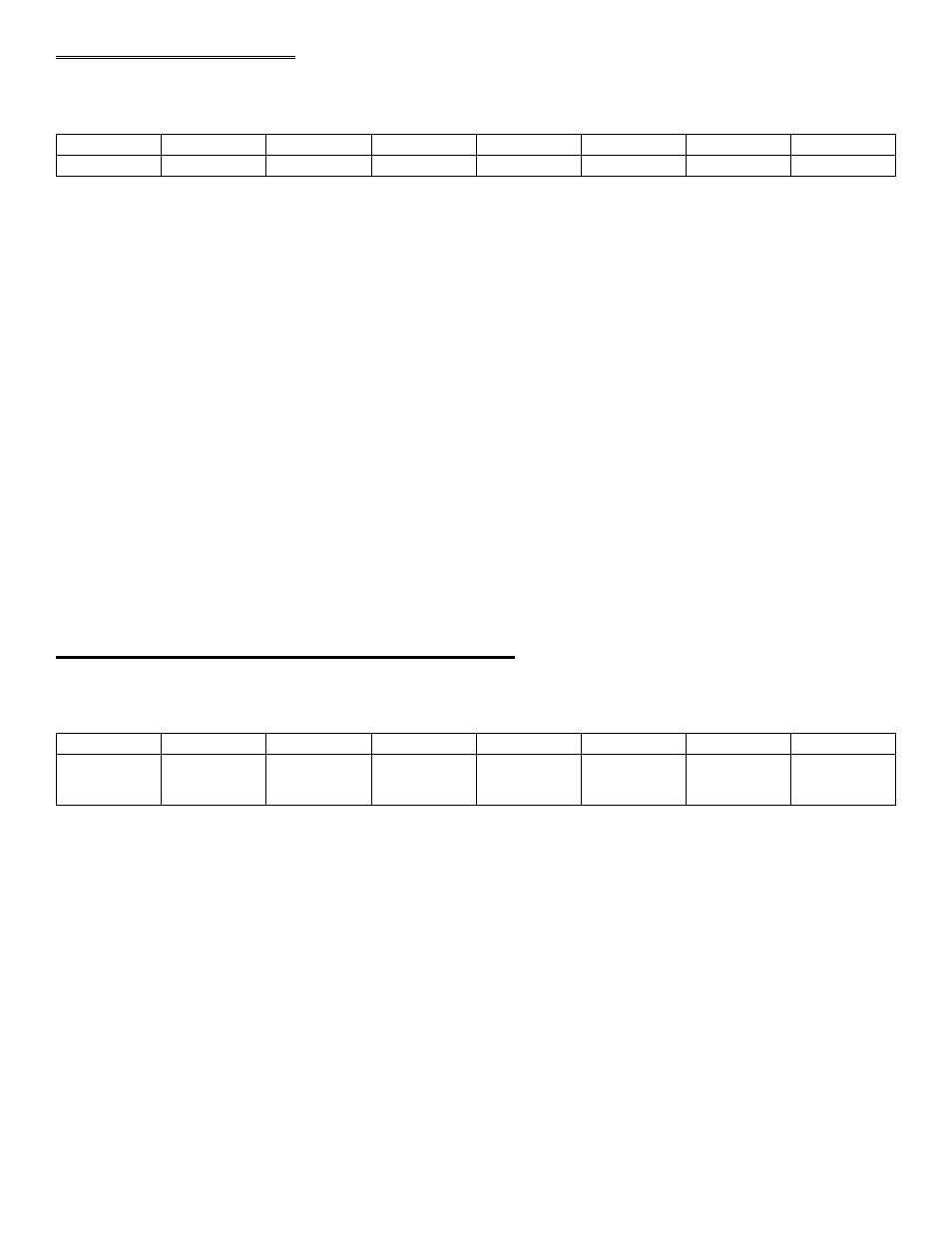

3.6 DMA, INTERRUPT & TRIGGER CONTROL

BASE ADDRESS + 9

TS0

TS1

DMA

Don’t

Care

IR1

IR2

IR4

INTE

0

1

2

3

4

5

6

7

A read and write register.

READ

INTE = 1, Interrupts are enabled. An interrupt generated will be placed on the PC bus interrupt level selected by IR4,

IR2 & IR1. INTE = 0, interrupts are disabled.

IR4, IR2, IR1 are bits in a binary number between 0 and 7 which map interrupts onto the PC bus interrupt levels 2 - 7.

Interrupts 0 & 1 may not be asserted by the CIO-DAS16Jr/16.

DMA = 1, DMA transfers are enabled. DMA = 0, DMA transfers are disabled. Note that this bit only allows the

board to assert a DMA request to the PC on the DMA request level selected by the DMA switch. Before this bit is

set to 1, the PC's 8237 (or appropriate) DMA controller chip must be set up.

TS1 & TS0 control the source of the A/D start conversion trigger according to Table 3-3 below.

14