5 register architecture 5.1 introduction – Measurement Computing CIO-DAS6402/12 User Manual

Page 18

5 REGISTER ARCHITECTURE

5.1

INTRODUCTION

The CIO-DAS6402 is controlled and monitored by reading and writing to 16 I/O addresses. The first address is referred to as the

BASE ADDRESS and is set by a bank of switches on the board. All other addresses are located at the BASE ADDRESS plus a

specified offset.

Registers are easy to read from and write to, though to create a complete data acquisition software program at the register level is a

significant undertaking. Unless there is a specific reason that you need to write your program at the register lever, we recommend

using our Universal Library.

In summary form, the registers and their function are listed on the following table. Within each register are eight bits which may

constitute a byte of data or be eight individual bit set/read functions.

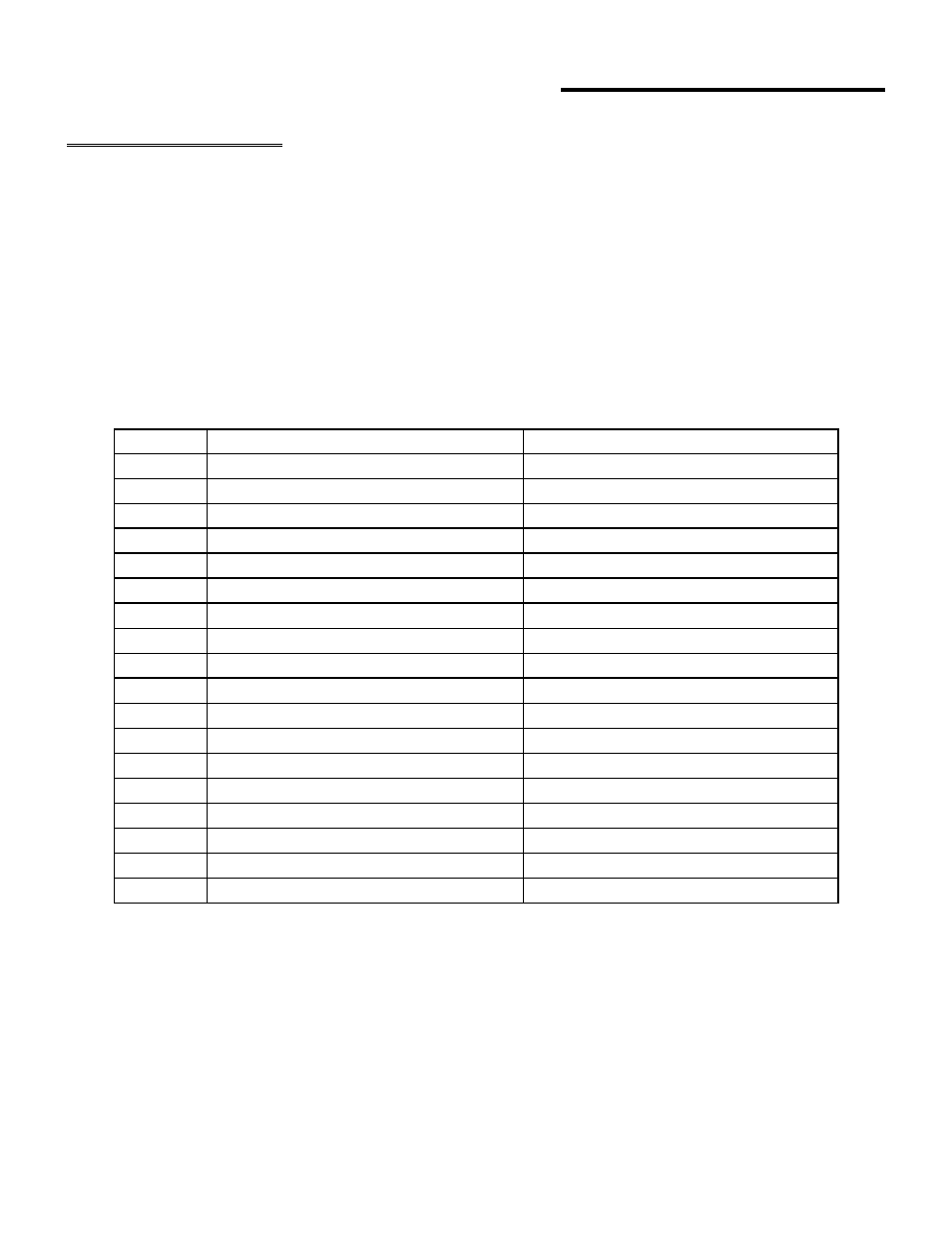

Table 5-1. DAS6402 I/O Map - COMPATIBLE Mode

(BOLD indicates register definition for DAS6402/16)

8254 Counter Control Register

None. No read back on 8254

BASE +15

CTR 2 Data - A/D Pacer Clock

CTR 2 Data - A/D Pacer Clock

BASE +14

CTR 1 Data - A/D Pacer Clock

CTR 1 Data - A/D Pacer Clock

BASE +13

Counter 0 Data

Counter 0 Data

BASE +12

MODE, A/D Gain Control

DMA, U/B, SEDIFF, MODE, A/D Gain

BASE +11

DAC range, TRIG0/CTR0

DAC range, TRIG0/CTR0

BASE +10

DMA Enable, Interrupt, Pacer Source

DMA Enable, Interrupt, Pacer Source

BASE + 9

Reset interrupt flip-flop

EOC, UNI/BIP, SEDIFF, Mux

BASE + 8

D/A 1 Bits 4-11

None

BASE + 7

D/A 1 Bits 0-3

None

BASE + 6

D/A 0 Bits 4-11

None

BASE + 5

D/A 0 Bits 0-3

None

BASE + 4

Digital Output Bits 0-3

Digital Input bits 0-3 / External control

BASE + 3

8/16 Channel Mux / Reset FIFO

8/16 Channel Mux

BASE + 2

None

A/D Bits 8 - 15 (MSB)

BASE + 1

Software Start A/D Conversion

A/D bits 0 (LSB) - 7

BASE

None

A/D Bits 4 -11 (MSB)

BASE + 1

Software Start A/D Conversion

A/D bits 0(LSB) - 3 & Channel #

BASE

WRITE FUNCTION

READ FUNCTION

ADDRESS

14