Watch-dog timer – Zilog Z8PE002 User Manual

Page 21

Z8PE002

ZiLOG

Z8Plus OTP Microcontroller

DS008700-Z8X0799

P R E L I M I N A R Y

21

WATCH-DOG TIMER

The Watch-Dog Timer (

WDT

) is a retriggerable one-shot

16-bit timer that resets the device

if it reaches its terminal

count. The

WDT

is driven by the

XTAL2

clock pin. To pro-

vide the longer time-out periods required in applications,

the watch-dog timer is only updated every 64th clock cycle.

When operating in the

RUN

or

HALT

modes, a

WDT

time-

out reset is functionally equivalent to an interrupt vectoring

the PC to

0020H

, and setting the

WDT

flag to

1

. Coming

out of

RESET

, the

WDT

is fully enabled with its time-out

value set at minimum, unless otherwise programmed during

the first instruction. Subsequent executions of the

WDT

in-

struction reinitialize the watch-dog timer registers (

C2h

and

C3h

) to their initial values as defined by bits

D6

,

D5

, and

D4

of the

TCTLHI

register. The

WDT

cannot be disabled ex-

cept on the first cycle after

RESET

and when the device en-

ters

STOP

mode.

The

WDT

instruction should be executed often enough to

provide some margin of time to allow the

WDT

registers to

approach

0

. Because the

WDT

time-out periods are rela-

tively long, a

WDT

RESET

occurs in the unlikely event that

the

WDT

times out on exactly the same cycle that the

WDT

instruction is executed.

RESET

clears both the

WDT

and

SMR

flags. A

WDT

time-

out sets the

WDT

flag, and the

STOP

instruction sets the

SMR

flag. This function enables software to determine

whether a

WDT

time-out or a return from

STOP

mode oc-

curred. Reading the

WDT

and

SMR

flags does not reset the

flag to

0

; therefore, the user must clear the flag via software.

Note: Failure to clear the

SMR

flag can result in unexpected

behavior.

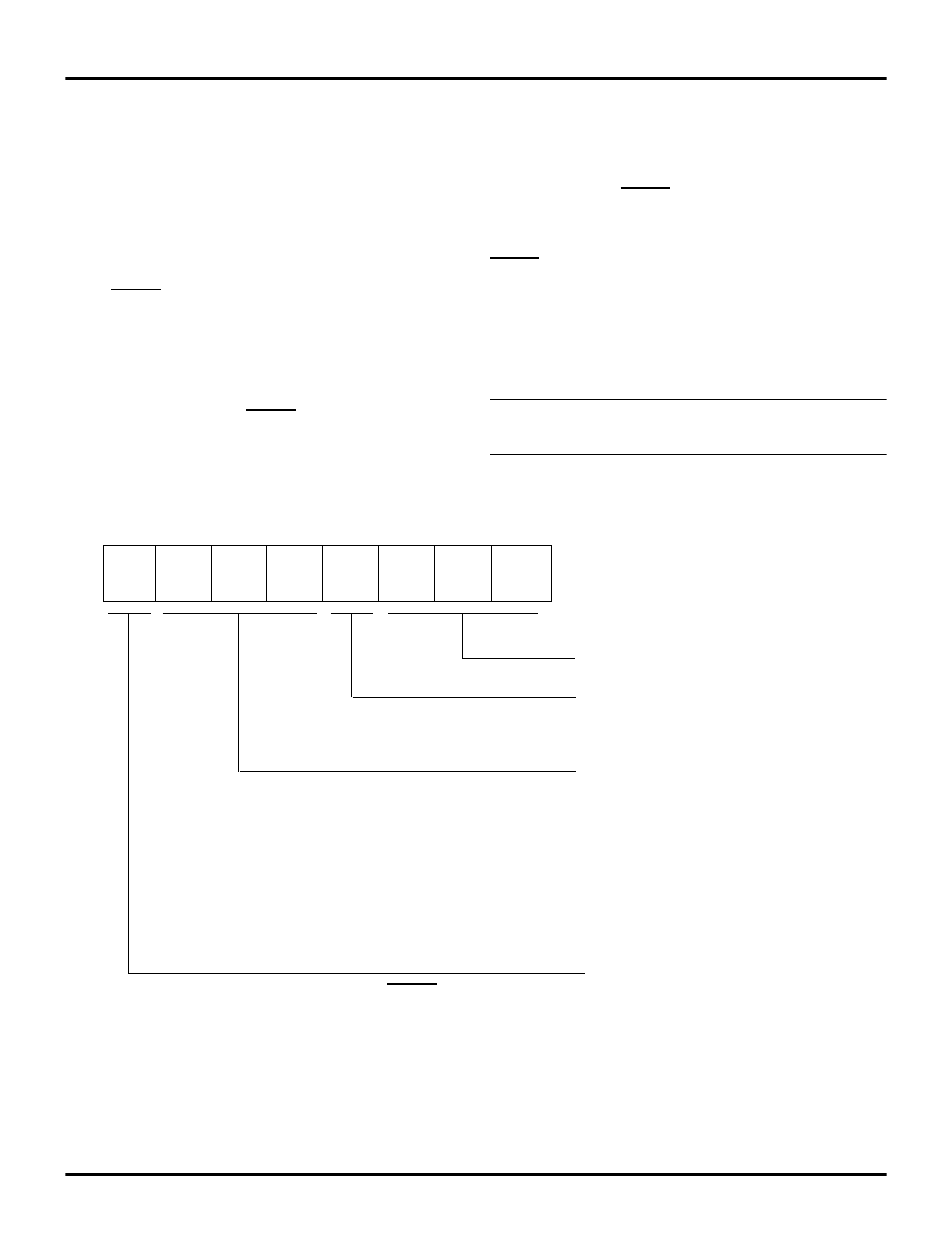

Figure 11. TCTLHI Register for Control of WDT

D7

D6

D5

D4

D3

D2

D1

D0

0C1

TCTLHI

Reserved (must be 0)

0 = STOP mode enabled

1 = STOP mode disabled*

D6 D5 D4 WDT TIMEOUT VALUE

---- ---- ---- --------------------------------

0 0 0 Disabled

0 0 1 65,536 TpC*

0 1 0 131,072 TpC

0 1 1 262,144 TpC

1 0 0 524,288 TpC

1 0 1 1,048,576 TpC

1 1 0 2,097,152 TpC

1 1 1 8,388,608 TpC

(XTAL clocks to time-out)

1 = WDT enabled in HALT mode*

0 = WDT disabled in HALT mode

*Designates the default value after RESET.