Z8pluscore, Reset – Zilog Z8PE002 User Manual

Page 15

Z8PE002

ZiLOG

Z8Plus OTP Microcontroller

DS008700-Z8X0799

P R E L I M I N A R Y

15

Z8PLUS CORE

The device is based on the ZiLOG Z8Plus Core Architec-

ture. This core is capable of addressing up to 32 KB of pro-

gram memory and 4 KB of RAM. Register RAM is accessed

as either 8- or 16-bit registers using a combination of 4-,

8-, and 12-bit addressing modes. The architecture supports

up to 15 vectored interrupts from external and internal

sources. The processor decodes 44 CISC instructions using

information.

RESET

This section describes the Z8Plus reset conditions, reset

timing, and register initialization procedures. Reset is gen-

erated by the Voltage Brown-Out/Power-On Reset

(

VBO/POR

), Watch-Dog Timer (

WDT

), and Stop-Mode

Recovery (

SMR

).

A system reset overrides all other operating conditions and

puts the Z8Plus device into a known state. To initialize the

chip’s internal logic, the

POR

device counts 64 internal

clock cycles after the oscillator stabilizes. The control reg-

isters and ports are not reset to their default conditions after

wakeup from a

STOP

mode or

WDT

time-out.

During

RESET

, the value of the program counter is

0020H

.

The I/O ports and control registers are configured to their

default reset state. Resetting the device does not affect the

contents of the general-purpose registers.

The

RESET

circuit initializes the control and peripheral reg-

isters, as shown in Table 8. Specific reset values are indi-

cated by a

1

or a

0

, while bits whose states are unchanged

or unknown from Power-Up are indicated by the letter

U

.

Program execution starts 10 External Crystal (

XTAL

) clock

cycles after the

POR

delay. The initial instruction fetch is

from location

0020H

. Figure 9 indicates reset timing.

After a reset, the first routine executed must be one that ini-

tializes the

TCTLHI

control register to the required system

configuration This activity is followed by initialization of

the remaining control registers.

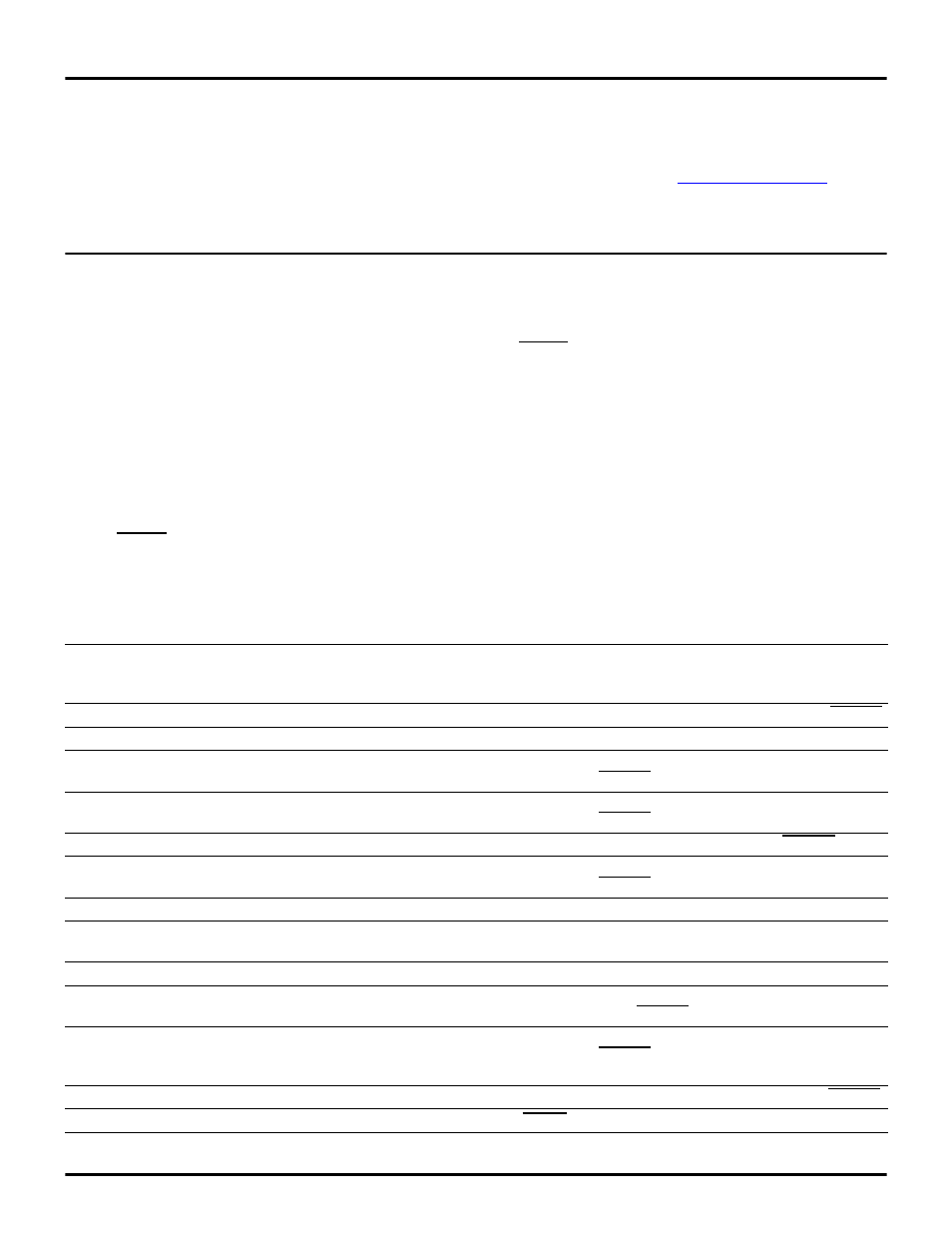

Table 8. Control and Peripheral Registers*

Register (HEX)

Register Name

Bits

Comments

7

6

5

4

3

2

1

0

FF

Stack Pointer

0

0

U

U

U

U

U

U Stack pointer is not affected by RESET.

FE

Reserved

FD

Register Pointer

U

U

U

U

0

0

0

0

Register pointer is not affected by

RESET.

FC

Flags

U

U

U

U

U

U

*

*

Only WDT & SMR flags are affected by

RESET.

FB

Interrupt Mask

0

0

0

0

0

0

0

0

All interrupts masked by RESET.

FA

Interrupt

Request

0

0

0

0

0

0

0

0

All interrupt requests cleared by

RESET.

F9–F0

Reserved

EF–E0

Virtual Copy

Virtual copy of the current working

register set.

DF–D8

Reserved

D7

Port B Special

Function

0

0

0

0

0

0

0

0

Deactivates all port special functions

after RESET.

D6

Port B

Directional

Control

0

0

0

0

0

0

0

0

Defines all bits as inputs in PortB after

RESET.

D5

Port B Output

U

U

U

U

U

U

U

U Output register not affected by RESET.

Note:

*The SMR and WDT flags are set to indicate the source of the RESET.