Zilog Z8PE002 User Manual

Page 16

Z8PE002

Z8Plus OTP Microcontroller

ZiLOG

16

P R E L I M I N A R Y

DS008700-Z8X0799

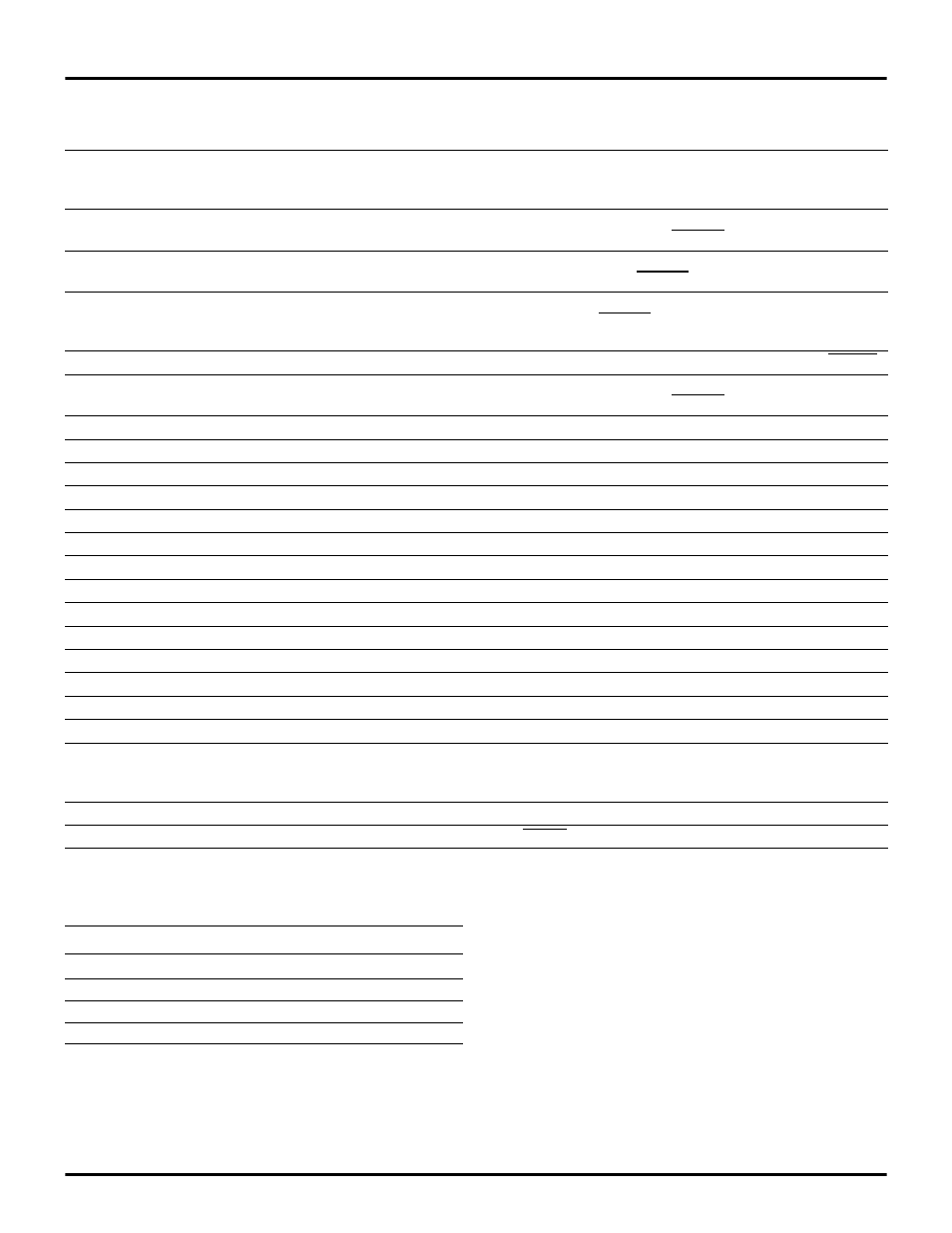

RESET (Continued)

D4

Port B Input

U

U

U

U

U

U

U

U Current sample of the input pin

following RESET.

D3

Port A Special

Function

0

0

0

0

0

0

0

0

Deactivates all port special functions

after RESET.

D2

Port A

Directional

Control

0

0

0

0

0

0

0

0

Defines all bits as inputs in PortA after

RESET.

D1

Port A Output

U

U

U

U

U

U

U

U Output register not affected by RESET

D0

Port A Input

U

U

U

U

U

U

U

U Current sample of the input pin

following RESET.

CF

Reserved

CE

Reserved

CD

T1VAL

U

U

U

U

U

U

U

U

CC

T0VAL

U

U

U

U

U

U

U

U

CB

T3VAL

U

U

U

U

U

U

U

U

CA

T2VAL

U

U

U

U

U

U

U

U

C9

T3AR

U

U

U

U

U

U

U

U

C8

T2AR

U

U

U

U

U

U

U

U

C7

T1ARHI

U

U

U

U

U

U

U

U

C6

T0ARHI

U

U

U

U

U

U

U

U

C5

T1ARLO

U

U

U

U

U

U

U

U

C4

T0ARLO

U

U

U

U

U

U

U

U

C3

WDTHI

1

1

1

1

1

1

1

1

C2

WDTLO

1

1

1

1

1

1

1

1

C1

TCTLHI

1

1

1

1

1

0

0

0

WDT enabled in HALT mode, WDT

time-out at maximum value, STOP

mode disabled.

C0

TCTLLO

0

0

0

0

0

0

0

0

All standard timers are disabled.

Table 8. Control and Peripheral Registers* (Continued)

Register (HEX)

Register Name

Bits

Comments

7

6

5

4

3

2

1

0

Note:

*The SMR and WDT flags are set to indicate the source of the RESET.

Table 9. Flag Register Bit D1, D0

D1

D0

Reset Source

0

0

V

BO

/POR

0

1

SMR Recovery

1

0

WDT Reset

1

1

Reserved