Zilog Z8PE002 User Manual

Page 19

Z8PE002

ZiLOG

Z8Plus OTP Microcontroller

DS008700-Z8X0799

P R E L I M I N A R Y

19

Interrupt Request (IREQ) Register Initialization

IREQ

(Table 12) is a register that stores the interrupt re-

quests for both vectored and polled interrupts. When an in-

terrupt is issued, the corresponding bit position in the reg-

ister is set to

1

. Bits

0

to

5

are assigned to interrupt requests

IREQ0

to

IREQ5

, respectively.

Whenever

RESET

is executed, the

IREQ

resistor is set to

00h

.

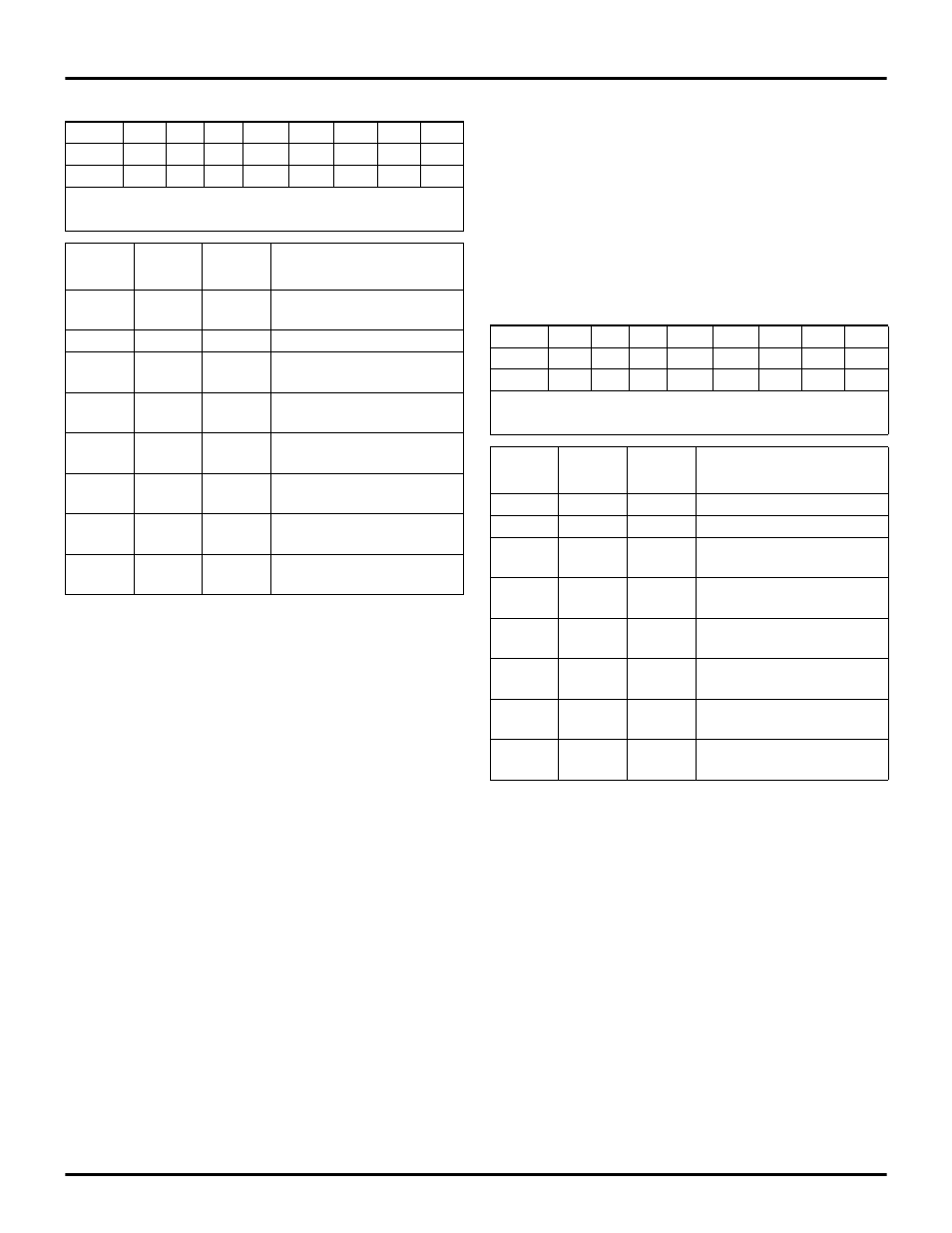

Table 11. Interrupt Mask Register—IMASK (FBh)

Bit

7

6

5

4

3

2

1

0

R/W

R/W R/W R/W R/W

R/W R/W R/W R/W

Reset

0

0

0

0

0

0

0

0

R = Read W = Write X = Indeterminate U = Undefined/

Undetermined

Bit

Position

R/W

Value

Description

7

0

1

Disables Interrupts

Enables Interrupts

6

0

Reserved, must be 0

5

0

1

Disables IRQ5

Enables IRQ5

4

0

1

Disables IRQ4

Enables IRQ4

3

0

1

Disables IRQ3

Enables IRQ3

2

0

1

Disables IRQ2

Enables IRQ2

1

0

1

Disables IRQ1

Enables IRQ1

0

0

1

Disables IRQ0

Enables IRQ0

Table 12. Interrupt Request Register–IREQ (FAh)

Bit

7

6

5

4

3

2

1

0

R/W

R/W R/W R/W R/W

R/W R/W R/W R/W

Reset

0

0

0

0

0

0

0

0

R = Read W = Write X = Indeterminate U = Undefined/

Undetermined

Bit

Position

R/W

Value

Description

7

R/W

0

Reserved, must be 0

6

R/W

0

Reserved, must be 0

5

R/W

0

1

IRQ5 reset

IRQ5 set

4

R/W

0

1

IRQ4 reset

IRQ4 set

3

R/W

0

1

IRQ3 reset

IRQ3 set

2

R/W

0

1

IRQ2 reset

IRQ2 set

1

R/W

0

1

IRQ1 reset

IRQ1 set

0

R/W

0

1

IRQ0 reset

IRQ0 set