The cyclone ep1c20 device, The cyclone ep1c20 device –4, Figure 1–2 – Altera Nios Development Board User Manual

Page 12: Fineline bga

1–4

Altera

Corporation

Nios Development Board Reference Manual, Cyclone Edition

December 2004

The Cyclone EP1C20 Device

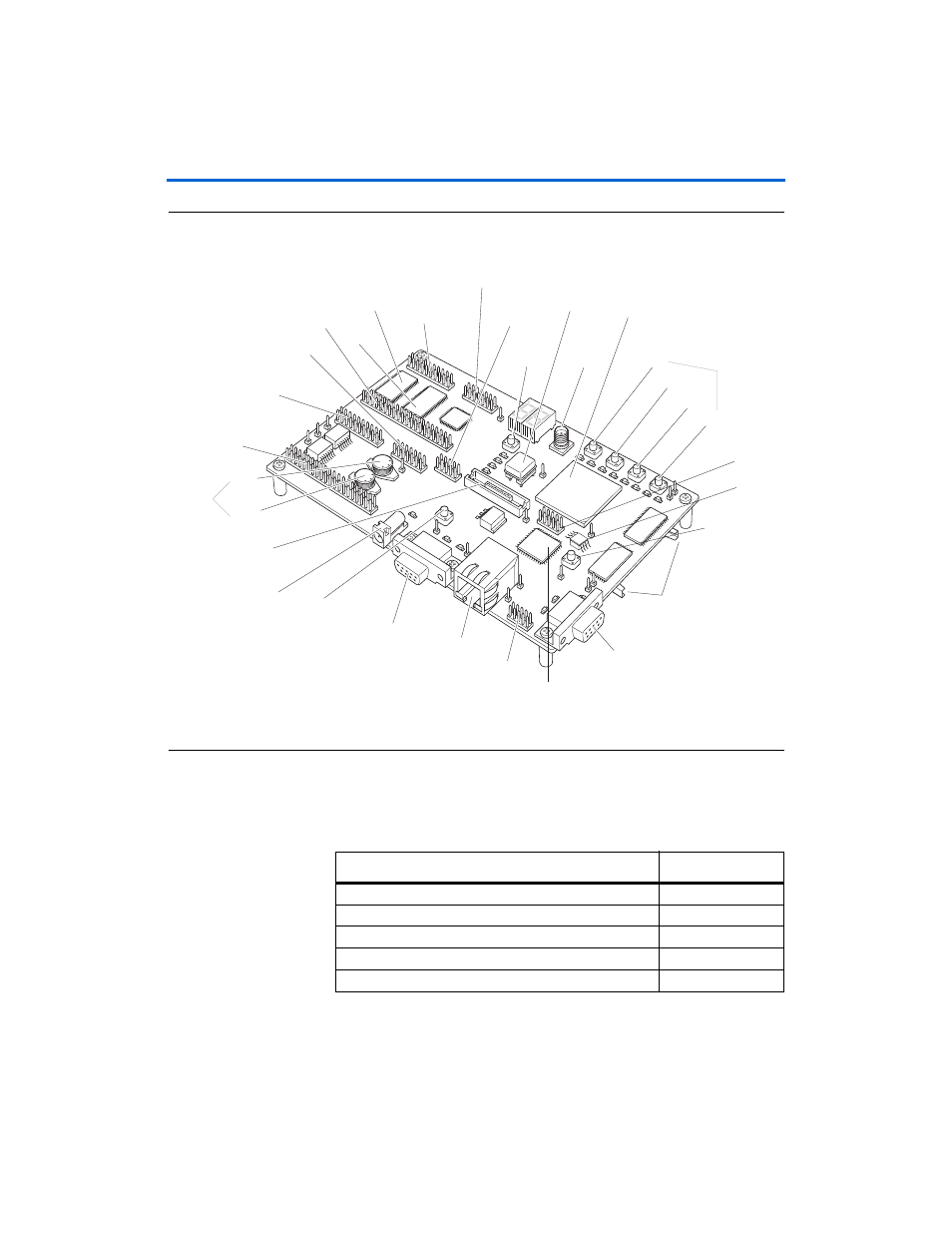

Figure 1–2. Nios Development Board Components

The Cyclone

EP1C20 Device

U60 is a Cyclone EP1C20F400C7 device in a 400-pin

FineLine BGA

®

package.

lists the Cyclone device features.

(J27)

Serial port

connector

(J19)

Serial port

connector

(RJ1)

RJ-45

connector

(J24)

10-pin JTAG

header for

Cyclone

FPGA

(J5)

10-pin JTAG

header for

MAX device

(J16)

40-pin header for

3.3 volt prototype

connector

(PROTO2)

(J12)

14-pin header for

5.0 volt prototype

connector

(PROTO1)

(J11)

40-pin header for

5.0 volt prototype

connector

(PROTO1)

(L11)

(L10)

(J25)

Debug mictor

connector

(SW10)

Power-On Reset

button

(J13)

20-pin header for

5.0 volt prototype

connector

(PROTO1)

(J15)

14-pin header for 3.3 volt

prototype connector

(PROTO2)

(J4)

External

clock

input

(J17)

20-pin header for

3.3 volt prototype

connector

(PROTO2)

(SW0)

(SW8)

CPU reset

button

(CON3)

CompactFlash

connector header

(SW1)

(SW2)

(SW3)

(SW9)

Safe Config

Button

(Y2)

Crystal

Oscillator

(U60)

Cyclone

EP1C20F400C7

device

(J26 )

DC jack

(SW3, SW2,

SW1, SW0)

User push-button

switches

(L11, L10)

Inductors

(U4)

Ethernet

PHY/MAC

device

(J28)

Serial flash

connector

(U59)

EPCS4

device

(U35)

SRAM

device

(U36)

SRAM

device

Table 1–1. Cyclone EP1C20 Device Features

Logic Elements

20,060

M4K RAM blocks (128 X 36 bits)

64

Total RAM bits

294,912

PLLs

2

Maximum user I/O pins

301