Clock worksheet, Clock worksheet -28 – Altera PowerPlay Early Power Estimator User Manual

Page 38

For more information about the PLLs of the supported device families, refer to the “Clock Networks and

PLLs“ chapter of the respective device handbook.

Clock Worksheet

Altera FPGA devices support global, regional, or periphery clock networks. The PowerPlay EPE

spreadsheet does not distinguish between global or regional clocks because the difference in power is not

significant.

Each row in the Clock worksheet of the PowerPlay EPE spreadsheet represents a clock network or a

separate clock domain. Enter the following parameters for each design module:

• Clock frequency (in MHz)

• Total fanout for each clock network used

• Global clock enable percentage

• Local clock enable percentage

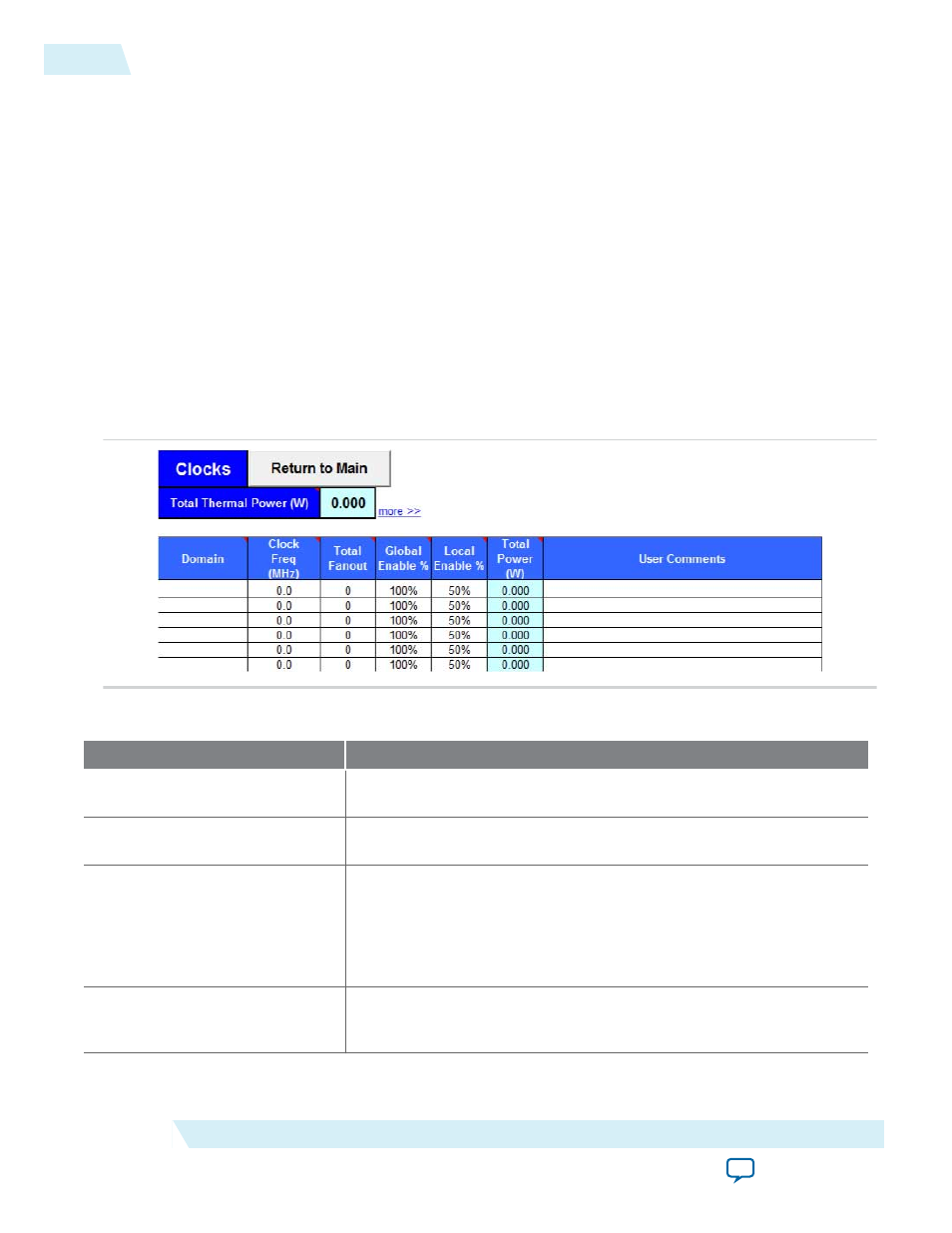

Figure 3-21: Clock Worksheet of the PowerPlay EPE Spreadsheet

Table 3-11: Clock Worksheet Information

Column Heading

Description

Domain

Specify a name for the clock network in this column. This is an

optional value.

Clock Freq (MHz)

Enter the frequency of the clock domain. This value is limited by the

maximum frequency specification for the device family.

Total Fanout

Enter the total number of flipflops and RAM, DSP, and I/O blocks fed

by this clock. The number of resources driven by every global clock

and regional clock signal is reported in the Fan-out column of the

Quartus II Compilation Report. In the Compilation Report, select

Fitter and click Resources Section. Select Global and Other Fast

Signals and click Fan-out.

Global Enable %

Enter the average percentage of time that the entire clock tree is

enabled. Each global clock buffer has an enable signal that you can use

to dynamically shut down the entire clock tree.

3-28

Clock Worksheet

UG-01070

2015.01.20

Altera Corporation

PowerPlay Early Power Estimator Worksheets