Altera PowerPlay Early Power Estimator User Manual

Page 25

Altera Corporation

3–11

May 2008

PowerPlay Early Power Estimator For Arria GX FPGAs

Using the PowerPlay Early Power Estimator

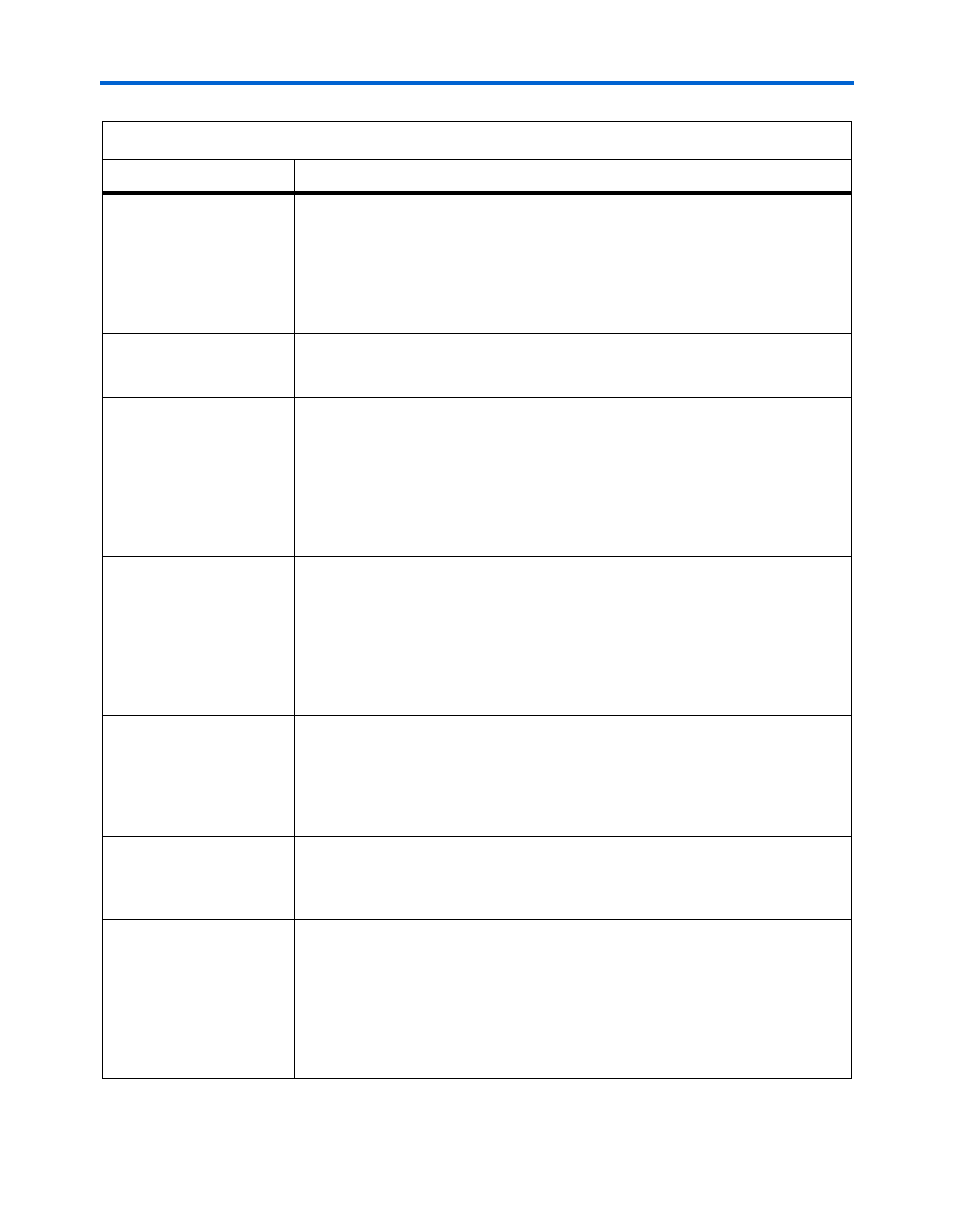

Port A – Write %

Enter the average percentage of time port A of the RAM block is in write mode

versus read mode. For simple dual-port (1R/1W) RAMs, the write port (A) is

inactive when not executing a write. For single-port and true dual-port RAMs, port

A reads when not written to. This field is ignored for RAMs in ROM mode.

This value must be a percentage number between 0% and 100%. The default is

50%.

Port B – Clock Freq

Enter the clock frequency for port B of the RAM block(s) in MHz. This value is

limited by the maximum frequency specification for the RAM type and device

family. Port B is ignored for RAM blocks in ROM or single-port mode.

Port B – Enable %

Enter the average percentage of time the input clock enable for port B is active,

regardless of activity on RAM data and address inputs. The enable percentage

ranges from 0 to 100%. The default is set to 25%. Port B is ignored for RAM blocks

in ROM or single-port mode.

RAM power is primarily consumed when a clock event occurs. Using a clock enable

signal to disable a port when no read or write operation is occurring can result in

significant power savings.

Port B – R/W %

For RAM blocks in true dual-port mode, enter the average percentage of time port

B of the RAM block is in write mode versus read mode. For RAM blocks in simple

dual-port mode, enter the percentage of time port B of the RAM block is reading.

You cannot write to port B in simple dual-port mode. Port B is ignored for RAM

blocks in ROM or single-port mode.

This value must be a percentage number between 0% and 100%. The default is

50%.

Toggle%

The average percentage of clock cycles that each block output signal changes

value. Multiplied by clock frequency to determine the number of transitions per

second. This value only affects routing power.

50% corresponds to a randomly changing signal. A random signal changes states

only half the time.

Valid Width/Mode

This check fails if the entered data width or RAM mode is not compatible with the

selected RAM type. M512s do not support true dual-port mode and M-RAMs do not

support ROM mode. See the description of the data width column for the range of

available widths for each RAM type.

Routing

This shows the power dissipation due to estimated routing (in W).

Routing power is highly dependent on placement and routing, which is itself a

function of design complexity. The values shown are representative of routing

power based on experimentation on over 100 customer designs.

Use the Quartus II PowerPlay Power Analyzer for detailed analysis based on the

routing used in your design. This value is calculated automatically.

Table 3–3. RAM Section Information (Part 3 of 4)

Column Heading

Description