Altera PowerPlay Early Power Estimator User Manual

Page 20

3–6

Altera

Corporation

PowerPlay Early Power Estimator For Arria GX FPGAs

May 2008

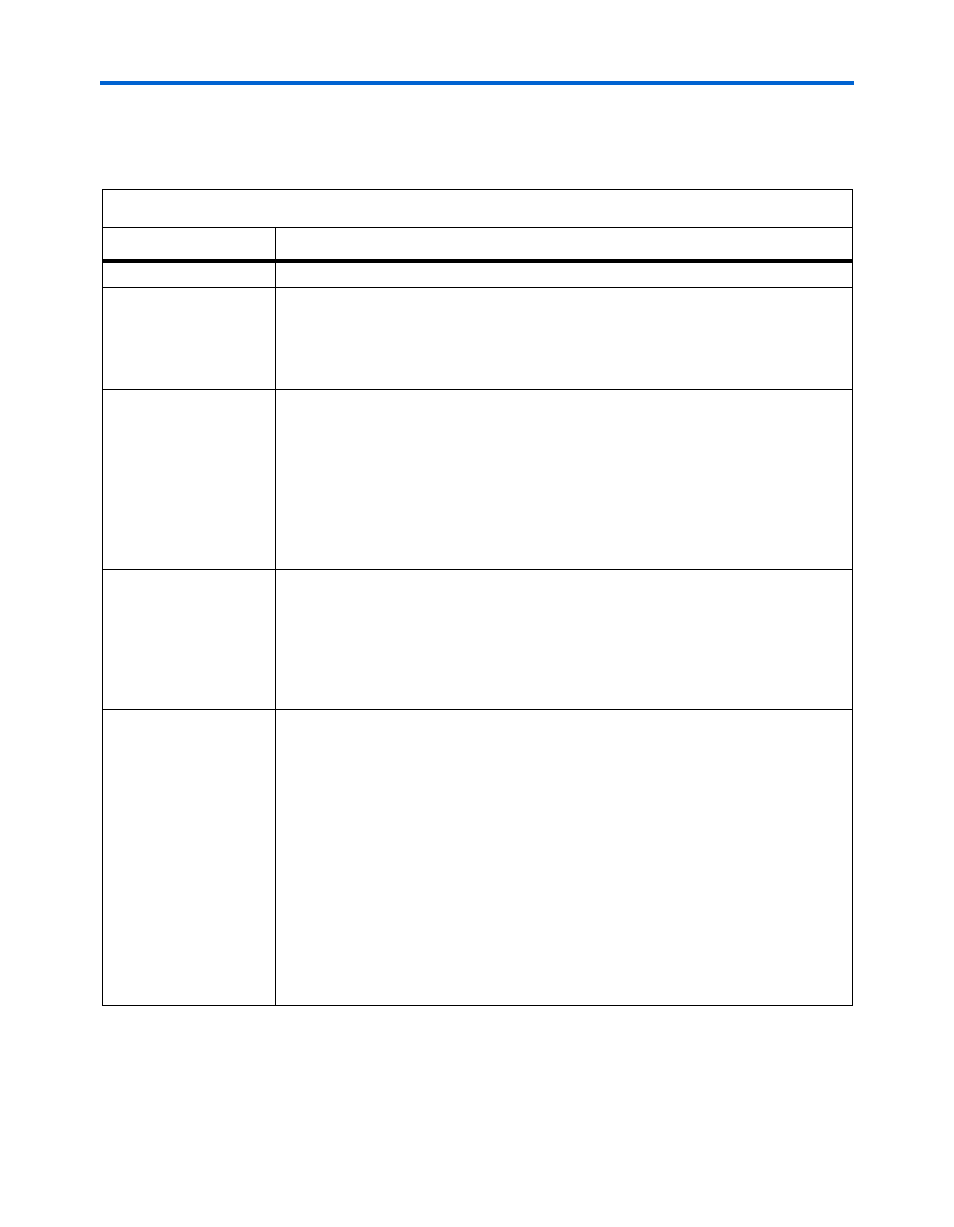

PowerPlay Early Power Estimator Inputs

Table 3–2

describes the values that need to be entered in the Logic section

of the PowerPlay Early Power Estimator.

Table 3–2. Logic Section Information (Part 1 of 2)

Column Heading

Description

Module

Enter a name for each module of the design.

Clock Frequency (MHz)

Enter a clock frequency (in MHz). This value is limited by the maximum frequency for

the device family.

100 MHz with a 12.5% toggle means that each LUT or flip flop output toggles

12.5 million times per second (100 × 12.5%).

#Combinational ALUTs Enter the number of combinational ALUTs.

For Arria

TM

GX this is the Combinational ALUTs value from the Quartus II Compilation

Report Usage Summary section.

Each Arria GX Adaptive Logic Module (ALM) contains up to two combinational ALUTs.

Smaller ALUTs consume less power than larger ALUTs, but the device can fit more of

them. The total number of ALUTs in the design should not exceed (number of ALMs)

× 2.

# FFs

Enter the number of flip flops in the module.

For Arria GX this is the dedicated logic registers value from the Quartus II Compilation

Report Usage Summary section.

Clock routing power is calculated separately on the Clocks section of the PowerPlay

Early Power Estimator.

Toggle %

Enter the average percentage of logic toggling on each clock cycle. The toggle

percentage ranges from 0 to 100%. Typically, the toggle percentage is 12.5%, which

is the toggle percentage of a 16-bit counter. To ensure you do not underestimate the

toggle percentage, you can use a higher toggle percentage. Most logic only toggles

infrequently, and hence toggle rates of less than 50% are more realistic.

For example, a TFF with its input tied to V

CC

has a toggle rate of 100% because its

output is changing logic states on every clock cycle (

Figure 3–2

).

Figure 3–3

shows

an example of a 4-bit counter. The first TFF with least significant bit (LSB) output

cout0

has a toggle rate of 100% because the signal toggles on every clock cycle.

The toggle rate for the second TFF with output

cout1

is 50% since the signal only

toggles on every two clock cycles. Consequently, the toggle rate for the third TFF with

output

cout2

and fourth TFF with output

cout3

are 25% and 12.5%, respectively.

Therefore, the average toggle percentage for this 4-bit counter is (100 + 50 + 25 +

12.5)/4 = 46.875%.