Altera PowerPlay Early Power Estimator User Manual

Page 21

Altera Corporation

3–7

May 2008

PowerPlay Early Power Estimator For Arria GX FPGAs

Using the PowerPlay Early Power Estimator

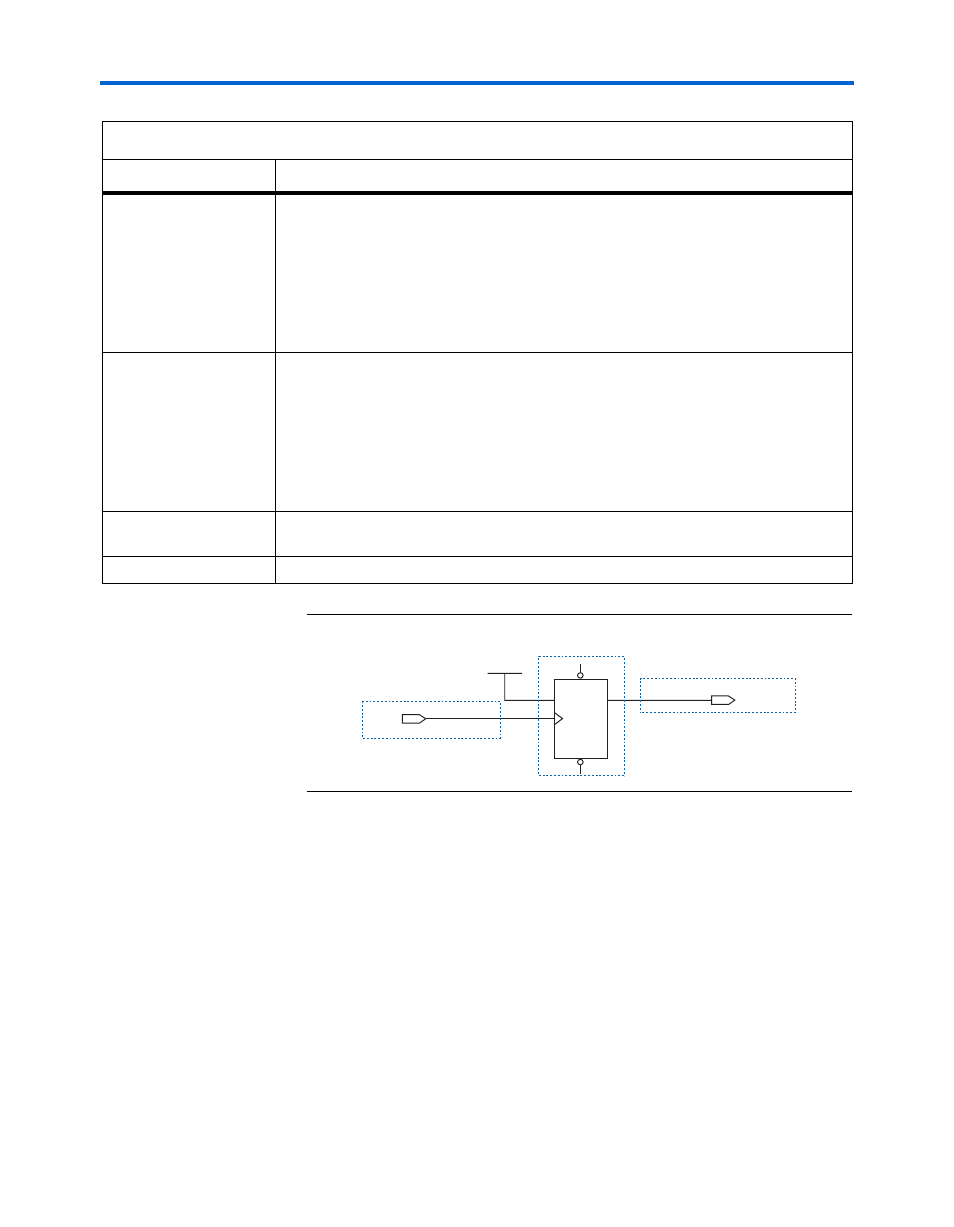

Figure 3–2. TFF Example

Routing

This shows the power dissipation due to estimated routing (in W).

Routing power is highly dependent on placement and routing, which is itself a function

of design complexity. The values shown are representative of routing power based on

experimentation on over 100 designs.

Use the Quartus II PowerPlay Power Analyzer for detailed analysis based on the

routing used in your design.

Block

This shows the power dissipation due to internal toggling of the ALMs (in W).

Logic block power is a function of the function implemented and relative toggle rates

of the various inputs. The PowerPlay Early Power Estimator spreadsheet uses an

estimate based on observed behavior across over 100 real-world designs.

Use the Quartus II PowerPlay Power Analyzer for accurate analysis based on the

exact synthesis of your design.

Total

This shows the total power dissipation (in W). The total power dissipation is the sum

of the routing and block power.

User Comments

Enter any comments. This is an optional entry.

Table 3–2. Logic Section Information (Part 2 of 2)

Column Heading

Description

PRN

CLRN

T

Q

TFF

clock

V

CC

INPUT

V

CC

OUTPUT

tff output