Altera Advanced SEU Detection IP Core User Manual

Page 4

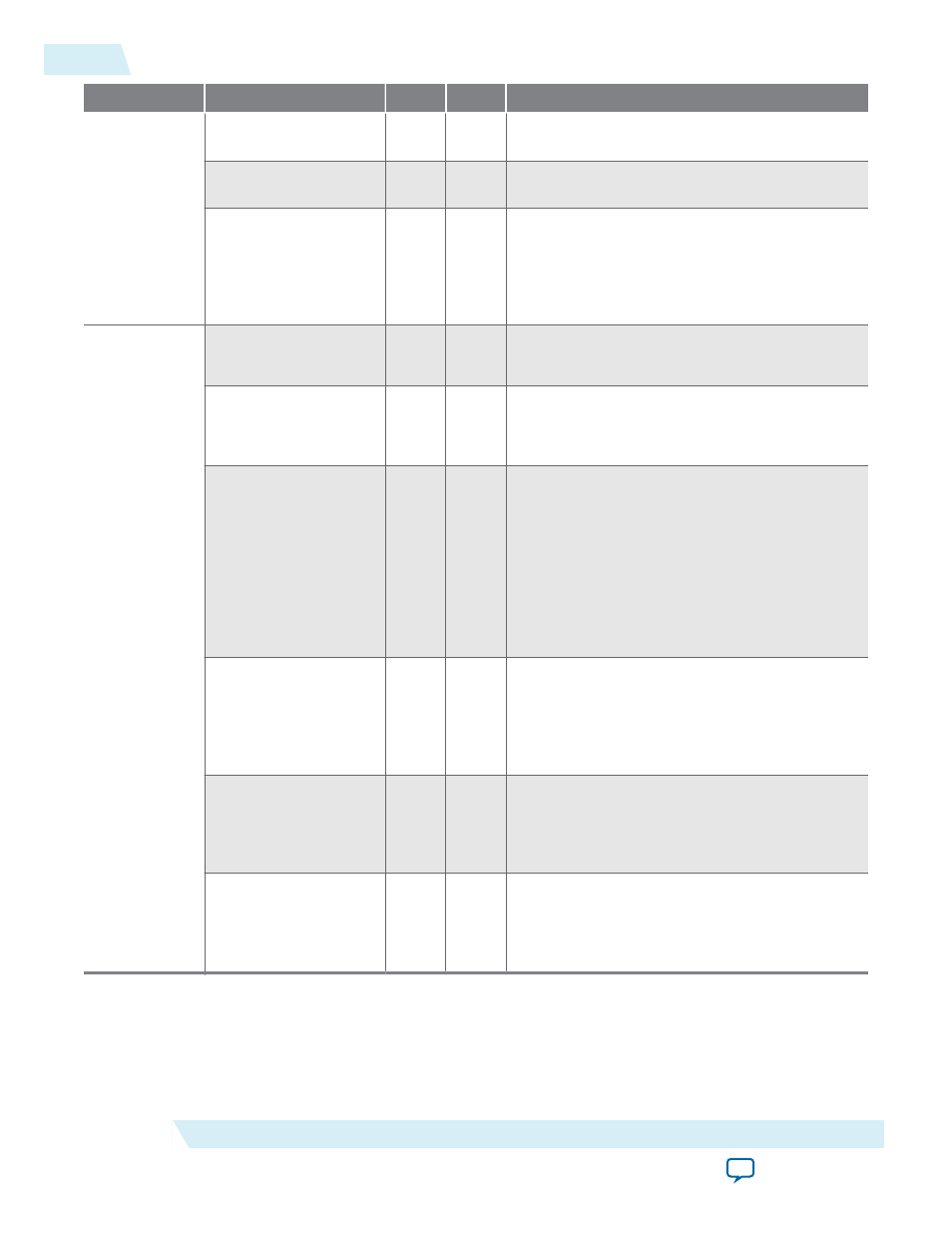

Interface

Signals

Type

Width

Description

Errors Output

noncritical_error

Outpu

t

1

Indicates that an SMH lookup determined that

the EDCRC error is in a non-critical region.

critical_error

Outpu

t

1

Indicates that an SMH lookup determined that

the EDCRC error is in a critical region.

regions_report

Outpu

t

1

• The ASD region for the error, as reported by

the SMH lookup.

• The width of this port comes from the

setting for the parameter “Largest ASD

region ID used.”

External

Memory

Avalon-MM

Master

mem_addr

Outpu

t

• Output to the user logic.

• Byte address of the 32-bit word to be read.

mem_rd

Outpu

t

• Output to the user logic.

• Signals to the user logic to request a read

operation.

mem_bytesel

Outpu

t

• Output to the user logic.

• A four-bit signal that selects the bytes

needed by the IP core. Use of this signal

allows 16-bit or 8-bit memories to optimize

the number of reads in cases where the IP

does not need all 32 bits. If bit 0 of mem_

bytesel is 0, then the IP core ignores bits 0 to

7 of mem_data, and similarly for bits 1 to 3

of mem_bytesel.

mem_wait

Input

• Input from the user logic.

• Signals to the memory interface that the

read operation is still running. Must be high

by the first rising clock after mem_rd is

asserted to hold the IP core in a wait state.

mem_data

Input

• Input from the user logic.

• 32-bit data bus. Data must be present if

mem_wait goes high and if mem_rd returns

low.

mem_datavalid

Input

• Input from the user logic.

• Signals that the mem_data signal contains

valid data in response to a previous mem_rd

request.

Related Information

4

On-Chip Processing Signals

ALTADVSEU

2015.05.04

Altera Corporation

Altera Advanced SEU Detection IP Core User Guide