Altera Advanced SEU Detection IP Core User Manual

Page 3

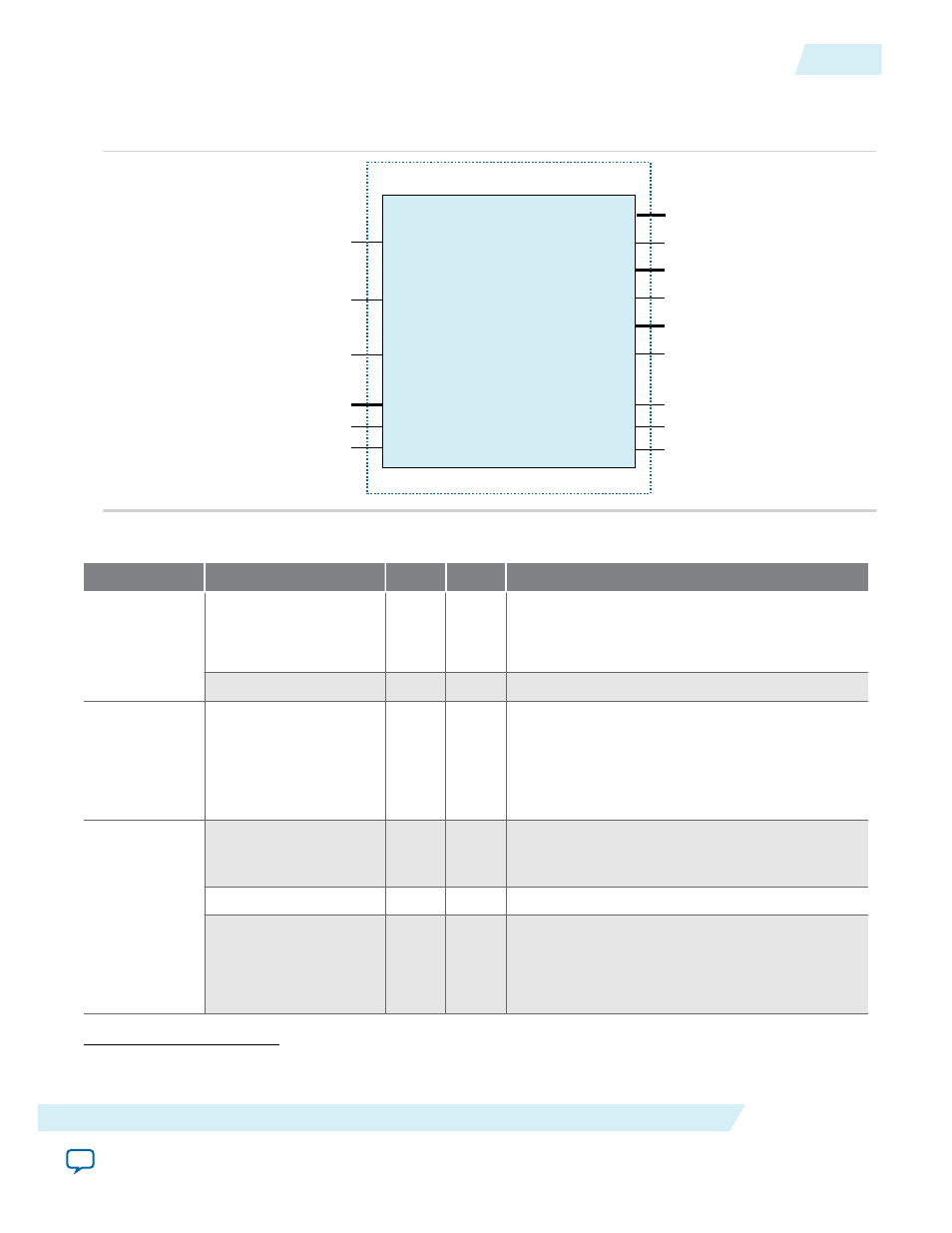

On-Chip Processing Signals

Figure 2: Altera Advanced SEU Detection Core Signals for On-Chip Processing

clk

reset

cache_comparison_off

data

valid

error

address

read

byteenable

waitrequest

critical_error

clk

reset

cache_comparison_off

emr[66:0]

emr_valid

emr_error

mem_addr[31:0]

mem_rd

mem_bytesel[3:0]

mem_wait

critical_error

my_asd

Altera Advanced SEU Detection IP Core

noncritical_error

noncritical_error

regions_report

regions_report

readdata

readdatavalid

mem_data[31:0]

mem_datavalid

Table 2: Altera Advanced SEU Detection Core Signals for On-Chip Processing

Interface

Signals

Type

Width

Description

Clock and reset

clk

Input

1

• Clock input.

• Recommended frequency is 100 MHz or

higher.

reset

Input

1

Active-high reset.

Cache Configu‐

ration

cache_comparison_off

Input

1

• Static input signal.

• Commands the IP core to bypass cache

comparison.

• You can use this signal with the internal

scrubbing feature for custom design.

Avalon-ST

(Streaming)

Sink Interface

Signals

(1)

emr

Input

67

Error Message Register data input from the

Altera Error Message Register Unloader IP

core.

emr_valid

Input

1

Indicates when emr data input is valid.

emr_error

Input

1

• Indicates when emr data will be ignored due

to an error.

• This may occur when there is a data overrun

from the Altera EMR Unloader IP core.

(1)

The Avalon (ST) Streaming Sink Interface should be connected to the corresponding Avalon-ST Source

Interface of the EMR Uploader IP Core.

ALTADVSEU

2015.05.04

On-Chip Processing Signals

3

Altera Advanced SEU Detection IP Core User Guide

Altera Corporation