Altera Advanced SEU Detection IP Core User Manual

Page 2

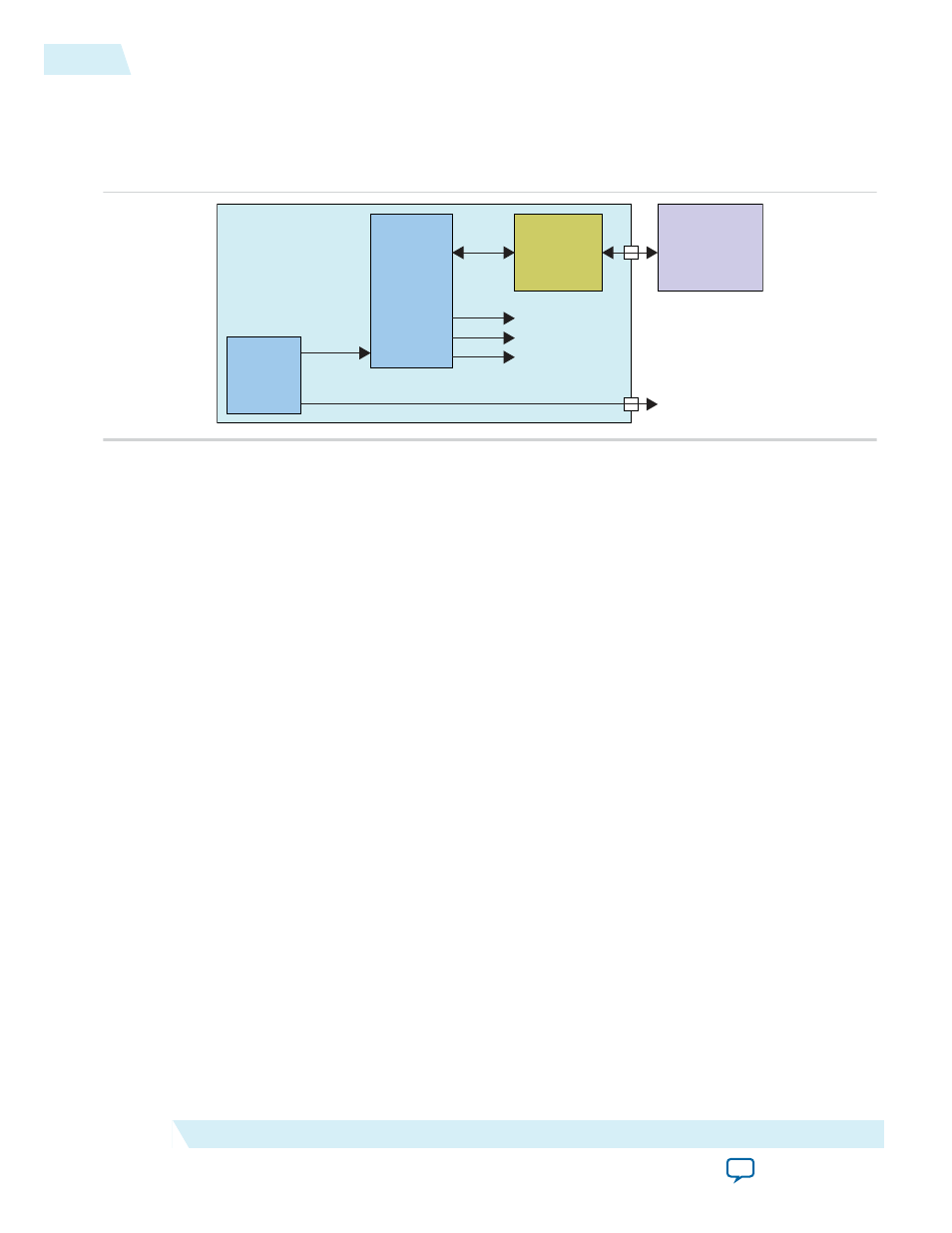

Altera Advanced SEU Detection IP core interprets the error detection register of the error detection block,

and then compares single-bit error locations with a sensitivity map. This check determines whether or not

the failure affects the device operation.

Figure 1: System Overview for On-Chip Lookup Sensitivity Processing

EMR

Unloader

IP Core

Advanced

SEU Detection

IP Core

User-Supplied

Memory Access

Logic

critical_error

noncritical_error

regions_report

Memory

Interface

Error

Messages

Register

Interface

CRAM CRC Error Detected

FPGA

Sensitivity Lookup

Information (SMH)

Stored in

External Memory

CRC_ERROR

The Altera Advanced SEU Detection IP core accepts the content of the error message register (EMR) and

issues a query to an external memory containing the sensitivity map. The system designer is responsible

for the memory access logic and external memory.

Altera recommends that you implement an SEU detection circuit that tolerates a soft error in its logic by

instantiating two instances of the Altera Advanced SEU Detection IP core in your design. In this case, one

instance of the IP core flags errors that occur in the other instance of the IP core as “critical.”

Related Information

•

Provides more information about the design security for Stratix IV devices.

•

Provides more information about the design security for Arria V devices.

•

Provides more information about the design security for Cyclone V devices.

•

Provides more information about the design security for Stratix V devices.

2

On-Chip Lookup Sensitivity Processing

ALTADVSEU

2015.05.04

Altera Corporation

Altera Advanced SEU Detection IP Core User Guide