Conclusion – Altera RAM-Based Shift Register User Manual

Page 19

Chapter 2: Getting Started

2–13

Conclusion

May 2013

Altera Corporation

RAM-Based Shift Register (ALTSHIFT_TAPS) Megafunction User Guide

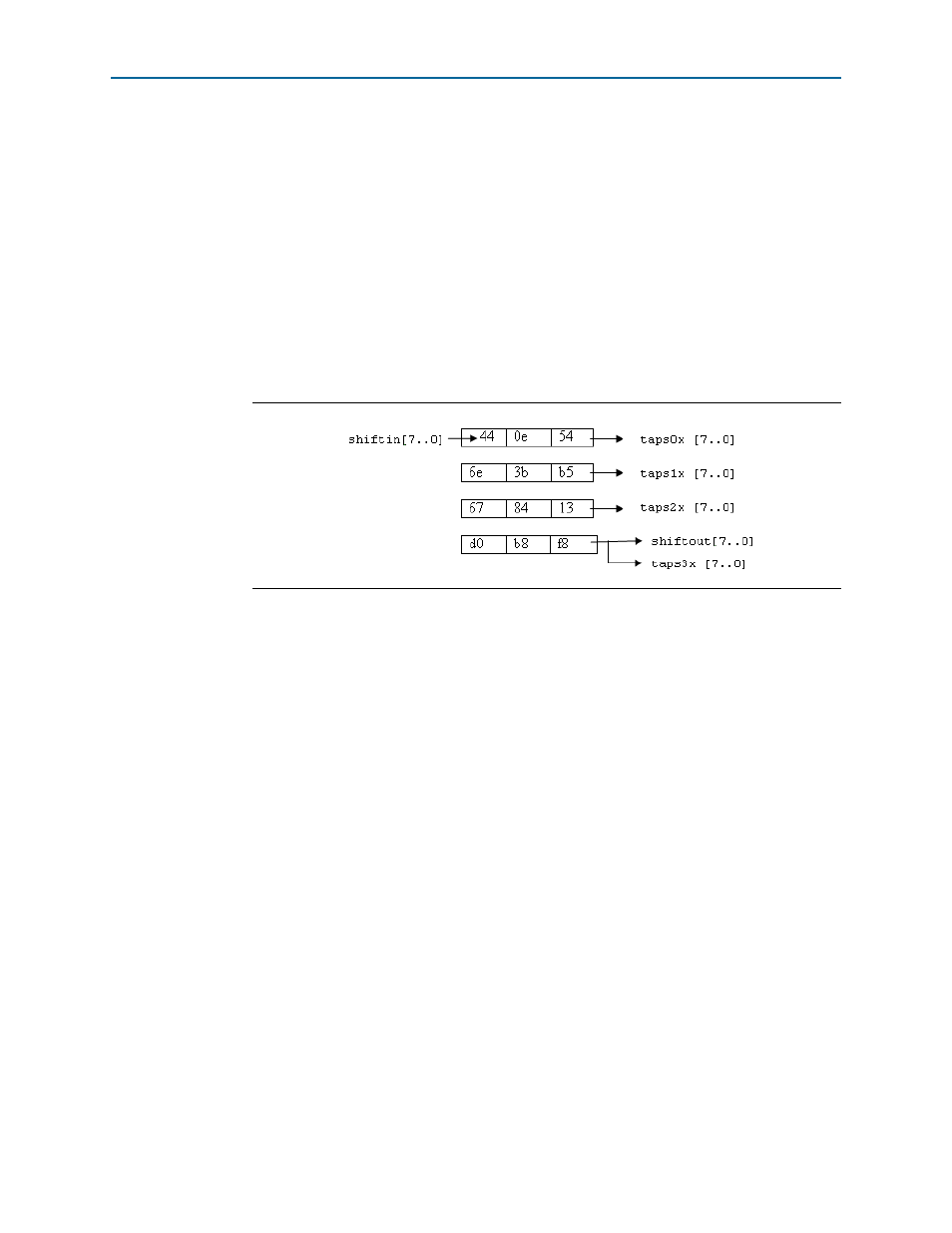

At 65 ns, the first data F8, and the fourth data 13 are shifted to taps1x and taps0x,

respectively. At 95 ns, the first data F8, the fourth data 13, and the seventh data B5 are

shifted to taps2x, taps1x, and taps0x, respectively. Finally, at 125 ns, all twelve data

words are shifted into the shift register. You can then start to tap the 1st-4th-7th-10th

data words simultaneously, from taps3x, taps2x, taps1x, and taps0x, respectively.

1

The shiftout output port is equivalent to taps3x and both ports generate the same

output data.

At the following rising clock edge, you can tap the 2nd-5th-8th-11th data words,

followed by the 3rd-6th-9th-12th data words at the next rising edge.

shows the contents for the shift register chain when all twelve words are being shifted

into the shift register.

After you have tapped out all the data at 155 ns, you can assert the aclr signal to

immediately clear all the data at the output ports and the contents of the shift register.

You can then start to shift in another twelve words of data.

1

This design example shows you how the shifting and tapping operation works. It is

not meant to show a specific application usage. You can use the tapping feature with

additional logic to suit your needs.

Conclusion

The shift register is widely used in digital signal processing (DSP) applications.

Compared to traditional shift registers that are implemented with standard flip-flops,

the ALTSHIFT_TAPS megafunction is more suitable for DSP applications, because the

megafunction is implemented using the embedded memory block, which saves logic

cells and routing resources, and provides a bigger memory capacity.

Also, the ALTSHIFT_TAPS megafunction is equipped with taps capabilities that allow

you to tap the data at certain fixed points. The selectable input data width, the length

of the taps, and the number of taps provide a flexible configuration of the shift register

you require.

Figure 2–14. Content of the Shift Register Chain at 125 ns