Altera RAM-Based Shift Register User Manual

Page 12

2–6

Chapter 2: Getting Started

Instantiating Megafunctions in HDL Code or Schematic Designs

RAM-Based Shift Register (ALTSHIFT_TAPS) Megafunction User Guide

May 2013

Altera Corporation

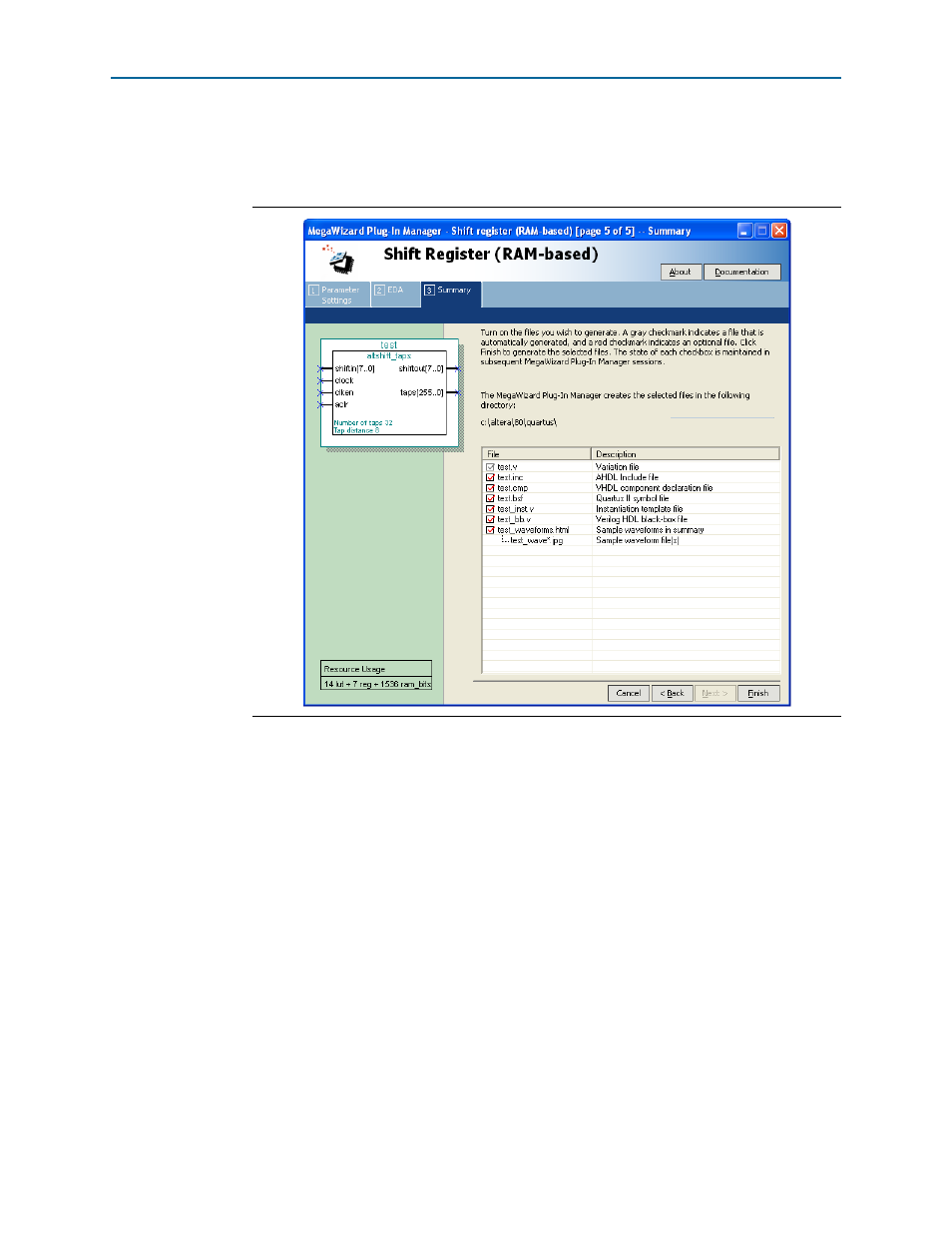

If you selected Generate netlist on page 4 of the MegaWizard Plug-In Manager, the

file for that netlist is also available. A gray checkmark indicates a file that is

automatically generated and a red checkmark indicates an optional file (

).

Instantiating Megafunctions in HDL Code or Schematic Designs

When you use the MegaWizard Plug-In Manager to customize and parameterize a

megafunction, it creates a set of output files that allows you to instantiate the

customized function in your design. Depending on the language you choose in the

MegaWizard Plug-In Manager, the wizard instantiates the megafunction with the

correct parameter values and generates a megafunction variation file (wrapper file) in

Verilog HDL (.v), VHDL (.vhd), or AHDL (.tdf), along with other supporting files.

The MegaWizard Plug-In Manager provides options to create the following files:

■

A sample instantiation template for the language of the variation file (_inst.v,

_inst.vhd

, or inst.tdf)

■

Component Declaration File (.cmp) that can be used in VHDL Design Files

■

AHDL Include File (.inc) that can be used in Text Design Files (.tdf)

■

Quartus II Block Symbol File (.bsf) that can be used in schematic designs

■

Verilog HDL module declaration file that can be used when instantiating the

megafunction as a black box in a third-party synthesis tool (_bb.v)

Figure 2–6. MegaWizard Plug-In Manager - Shift Register (RAM-based) [page 5 of 5]