Designing for interoperability – Echelon LonWorks Twisted Pair Control Module User Manual

Page 42

34

Design Issues

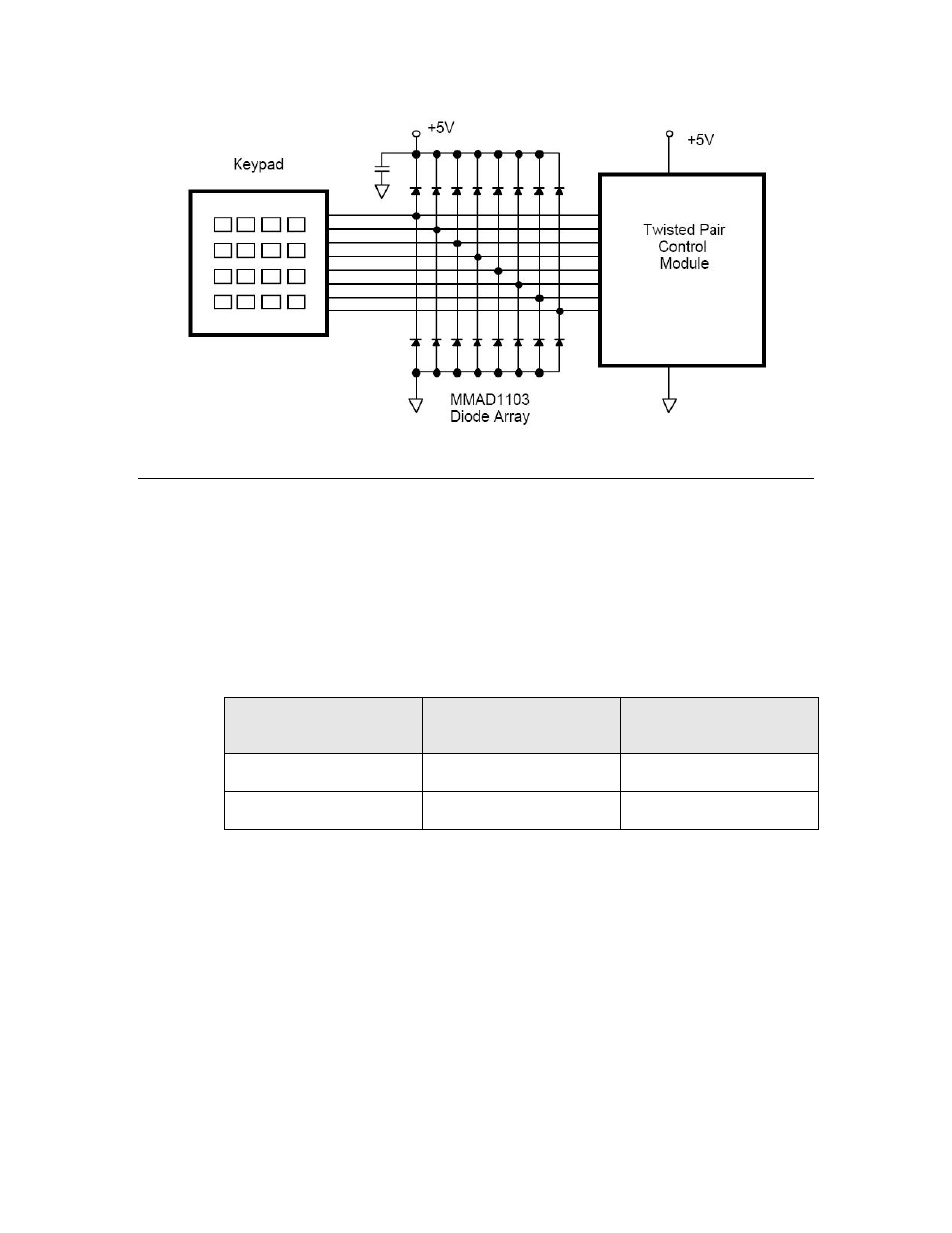

Figure 17. Example of Diode Clamping Protection for Control Module I/O Lines

Designing for Interoperability

To meet the L

ON

W

ORKS

interoperability guidelines for the Neuron 3150 TP/XF-

78, TP/XF-78F, and TP/XF-1250 devices, the following printed circuit layout

guideline for the application electronics board is recommended.

Mutual capacitance of data pair conductors (differential capacitance) from the

twisted pair medium tap connector to the connector which mates to the TP/XF

control module P2 header must be kept within the maximum limit specified in

Table 10. Mutual Capacitance of Data Pair Conductors

Module type

Maximum mutual

capacitance

Maximum PCB trace

lengths

TP/XF-78, -78F

5 pF

50 mm

TP/XF-1250

2 pF

20 mm