Maxim Integrated DS80C390 User Manual

Page 5

DS80C390

5 of 58

110199

58-64,

1

2-8, 10

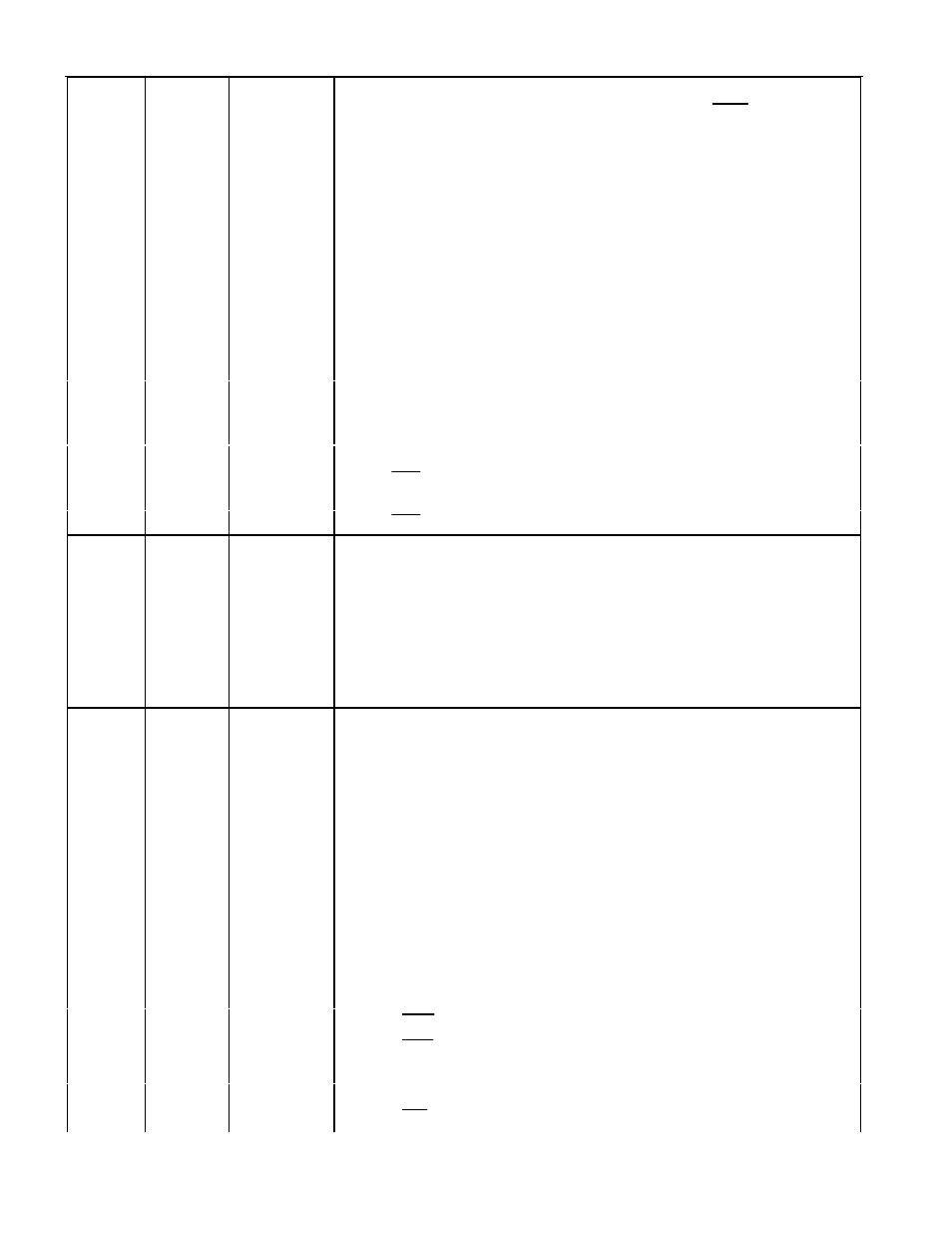

P1.0-P1.7

Port 1 - I/O. Port 1 can function as an 8-bit bi-directional I/O port,

the non-multiplexed A0 - A7 signals (when the

MUX

pin =1), and

as an alternate interface for internal resources. Setting the SP1EC

bit relocates RXD1 and TXD1 to Port 5. The reset condition of Port

1 is all bits at logic 1 via a weak pullup. The logic 1 state also

serves as an input mode, since external circuits writing to the port

can overdrive the weak pullup. When software clears any port pin

to 0, a strong pulldown is activated that remains on until either a 1

is written to the port pin or a reset occurs. Writing a 1 after the port

has been at 0 will activate a strong transition driver, followed by a

weaker sustaining pullup. Once the momentary strong driver turns

off, the port once again becomes the output (and input) high state.

Port Alternate Function

58

2

A0

P1.0 T2 External I/O for Timer/Counter 2

59

3

A1

P1.1 T2EX Timer/Counter 2 Capture/Reload Trigger

60

4

A2

P1.2 RXD1 Serial Port 1 Input

61

5

A3

P1.3 TXD1 Serial Port 1 Output

62

6

A4

P1.4 INT2 External Interrupt 2 (Pos. Edge Detect)

63

7

A5

P1.5

INT3

External Interrupt 3 (Neg. Edge Detect)

64

8

A6

P1.6 INT4 External Interrupt 4 (Pos. Edge Detect)

1

10

A7

P1.7

INT5

External Interrupt 5 (Neg. Edge Detect)

35

36

37

38

39

42

43

44

46

47

48

49

50

53

54

55

A8 (P2.0)

A9 (P2.1)

A10 (P2.2)

A11 (P2.3)

A12 (P2.4)

A13 (P2.5)

A14 (P2.6)

A15 (P2.7)

A15-A8 (Port 2) - Output. Port 2 serves as the MSB for external

addressing. The port automatically asserts the address MSB during

external ROM and RAM access. Although the Port 2 SFR exists,

the SFR value will never appear on the pins (due to memory

access). Therefore accessing the Port 2 SFR is only useful for

MOVX A, @Ri or MOVX @Ri, A instructions, which use the Port

2 SFR as the external address MSB.

4-7,

10-13

13-16,

19-22

P3.0-P3.7

Port 3 - I/O. Port 3 functions as an 8-bit bi-directional I/O port,

and as an alternate interface for several resources found on the

traditional 8051. The reset condition of Port 1 is all bits at logic 1

via a weak pullup. The logic 1 state also serves as an input mode,

since external circuits writing to the port can overdrive the weak

pullup. When software clears any port pin to 0, the device activates

a strong pulldown that remains on until either a 1 is written to the

port pin or a reset occurs. Writing a 1 after the port has been at 0

will activate a strong transition driver, followed by a weaker

sustaining pullup. Once the momentary strong driver turns off, the

port once again becomes the output (and input) high state.

Port

Alternate Function

4

13

P3.0

RXD0 Serial Port 0 Input

5

14

P3.1

TXD0 Serial Port 0 Output

6

15

P3.2

INT0

External Interrupt 0

7

16

P3.3

INT1

External Interrupt 1

10

19

P3.4

T0 Timer 0 External Input

11

20

P3.5

T1/XCLK Timer 1 External Input/External Clock Output

12

21

P3.6

WR

External Data Memory Write Strobe