Enhanced dual data pointers, Clock control and power management – Maxim Integrated DS80C390 User Manual

Page 16

DS80C390

16 of 58

110199

ENHANCED DUAL DATA POINTERS

The DS80C390 contains two data pointers, DPTR0 and DPTR1, designed to improve performance in

applications that require high data throughput. Incorporating a second data pointer allows the software to

greatly speed up block data (MOVX) moves by using one data pointer as a source register and the other

as the destination register.

DPTR0 is located at the same address as the original 8051 data pointer, allowing the DS80C390 to

execute standard 8051 code with no modifications. The second data pointer, DPTR1, is split between the

DPH1 and DPL1 SFRs, similar to the DPTR0 configuration. The active data pointer is selected with the

data pointer select bit SEL (DPS.0). Any instructions that reference the DPTR (i.e., MOVX A, @DPTR),

will select DPTR0 if SEL=0, and DPTR1 if SEL=1. Because the bits adjacent to SEL are not

implemented, the state of SEL (and thus the active data pointer) can be quickly toggled by the INC DPS

instruction without disturbing other bits in the DPS register.

Unlike the standard 8051, the DS80C390 has the ability to decrement as well as increment the data

pointers without additional instructions. When the INC DPTR instruction is executed, the active DPTR

increments or decrements according to the ID1, ID0 (DPS.7-6), and SEL (DPS.0) bits as shown. The

inactive DPTR is not affected.

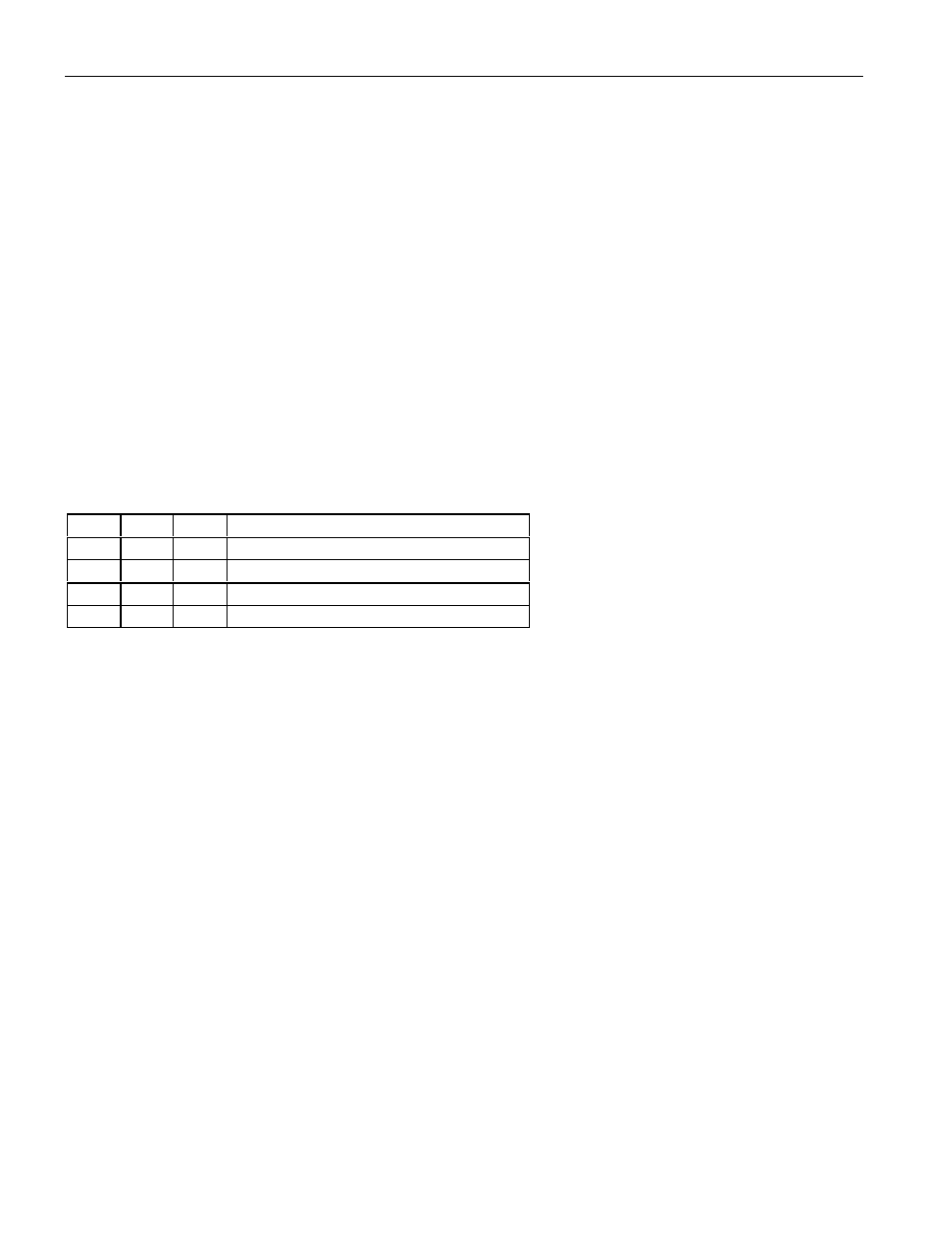

DATA POINTER AUTOINCREMENT/DECREMENT CONFIGURATION Table 9

ID1

ID0

SEL

Result of INC DPTR

X

0

0

Increment DPTR0

X

1

0

Decrement DPTR0

0

X

1

Increment DPTR1

1

X

1

Decrement DPTR1

Another useful feature of the device is its ability to automatically switch the active data pointer after a

DPTR-based instruction is executed. This feature can greatly reduce the software overhead associated

with data memory block moves, which toggle between the source and destination registers. When the

Toggle Select bit (TSL;DPS.5) is set to 1, the SEL bit (DPS.0) is automatically toggled every time one of

the following DPTR related instructions is executed.

INC DPTR

MOV DPTR, #data16

MOVC A, @A+DPTR

MOVX A, @DPTR

MOVX @DPTR, A

As a brief example, if TSL is set to 1, then both data pointers can be updated with two INC DPTR

instructions. Assume that SEL=0, making DPTR the active data pointer. The first INC DPTR increments

DPTR and toggles SEL to 1. The second instruction increments DPTR1 and toggles SEL back to 0.

INC DPTR

INC DPTR

CLOCK CONTROL AND POWER MANAGEMENT

The DS80C390 includes a number of unique features that allow flexibility in selecting system clock

sources and operating frequencies. To support the use of inexpensive crystals while allowing full speed

operation, a clock multiplier is included in the processor’s clock circuit. Also, in addition to the standard