On-chip arithmetic accelerator, Arithmetic accelerator execution times table 3 – Maxim Integrated DS80C390 User Manual

Page 10

DS80C390

10 of 58

110199

EIE

CANBIE

C0IE

C1IE

EWDI

EX5

EX4

EX3

EX2

E8h

MXAX

EAh

C1M1C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

EBh

C1M2C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

ECh

C1M3C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

EDh

C1M4C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

EEh

C1M5C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

EFh

B

F0h

C1M6C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

F3h

C1M7C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

F4h

C1M8C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

F5h

C1M9C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

F6h

C1M10C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

F7h

EIP

CANBIP

C0IP

C1IP

PWDI

PX5

PX4

PX3

PX2

F8h

C1M11C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

FBh

C1M12C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

FCh

C1M13C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

FDh

C1M14C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

FEh

C1M15C

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

FFh

*Shaded bits are Timed Access protected.

ON-CHIP ARITHMETIC ACCELERATOR

An on-chip math accelerator allows the microcontroller to perform 32- and 16-bit multiplication, division,

shifting, and normalization using dedicated hardware. Math operations are performed by sequentially

loading three special registers. The mathematical operation is determined by the sequence in which three

dedicated SFRs (MA, MB and MC) are accessed, eliminating the need for a special step to choose the

operation. The normalize function facilitates the conversion of 4-byte unsigned binary integers into

floating point format. The following table shows the operations supported by the math accelerator and

their time of execution.

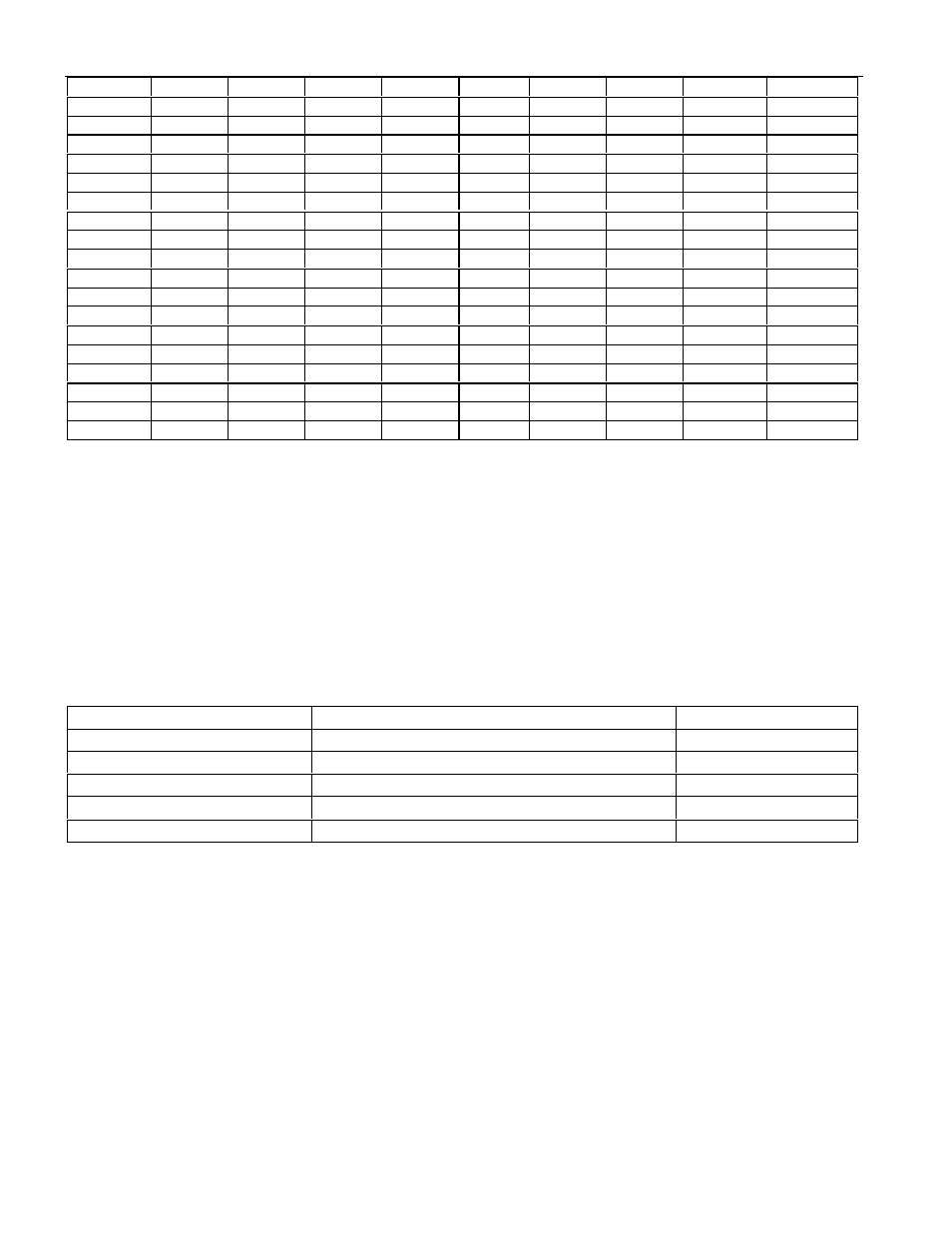

ARITHMETIC ACCELERATOR EXECUTION TIMES Table 3

Operation

Result

Execution Time

32-bit/16-bit divide

32-bit quotient, 16-bit remainder

36 t

CLCL

16-bit/16-bit divide

16-bit quotient, 16-bit remainder

24 t

CLCL

16-bit/16-bit multiply

32-bit product

24 t

CLCL

32-bit shift left/right

32-bit result

36 t

CLCL

32-bit normalize

32-bit mantissa, 5 bit exponent

36 t

CLCL

The following table demonstrates the procedure to perform mathematical operations using the hardware

math accelerator. The MA and MB registers must be loaded and read in the order shown for proper

operation, although accesses to any other registers can be performed between access to the MA or MB

registers. An access to the MA, MB, or MC registers out of sequence will corrupt the operation, requiring

the software to clear the MST bit to restart the math accelerator state machine. Consult the description of

the MCNT0 SFR for details of how the shift and normalize functions operate.