Digilent Basys Board Rev.C User Manual

Page 2

Digilent

Basys Reference Manual

www.digilentinc.com

Copyright Digilent, Inc.

Page 2/12

Doc: 502-107

Device Configuration

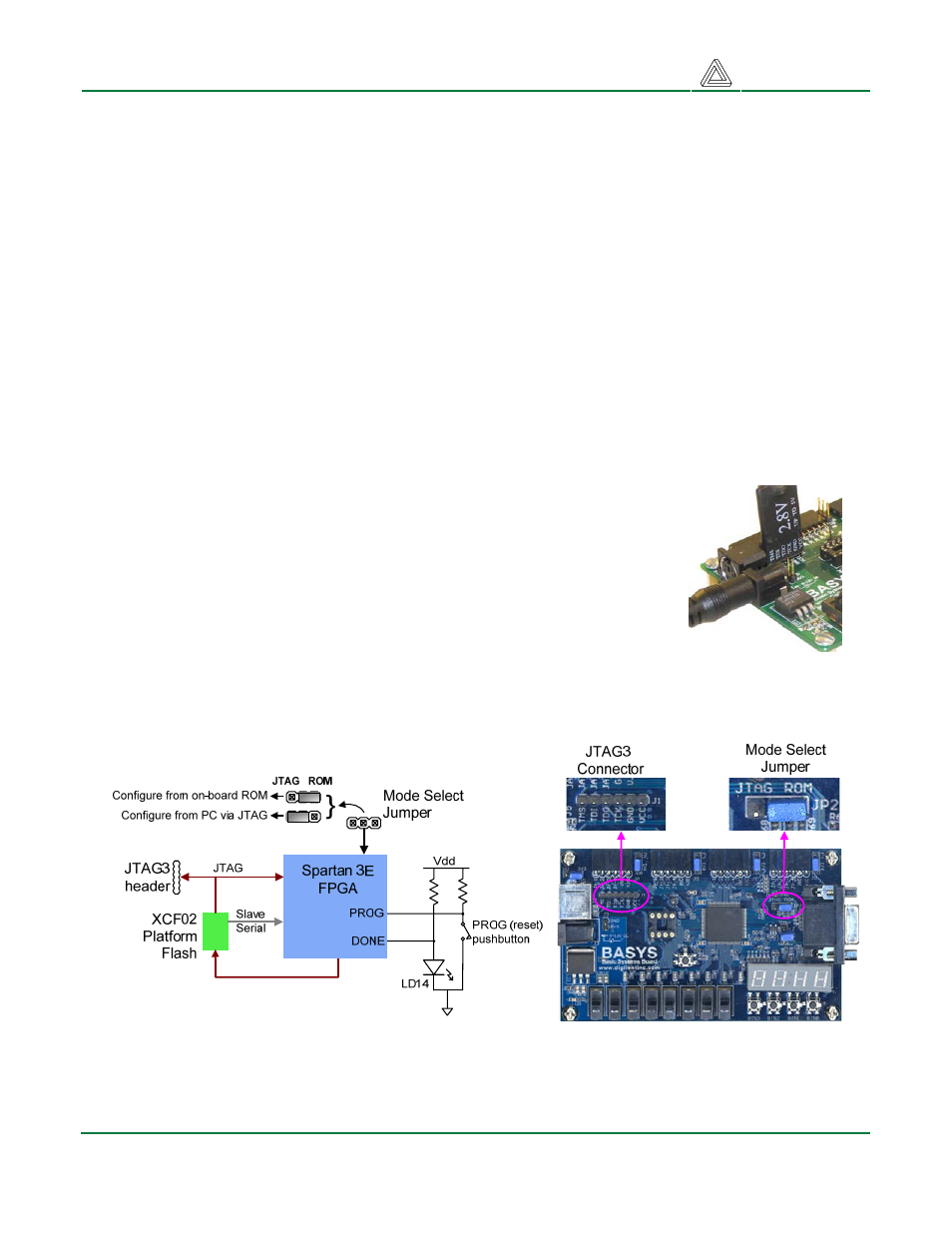

At power-on, the FPGA on the Basys board is not configured and performs no functions - it must be

configured (or programmed) by the user before it can perform any functions. Design software, like the

free WebPack from Xilinx, can be used to define any number of circuits that can be programmed into

the FPGA. Once programmed, the FPGA will retain its configuration only as long is power is applied.

The FPGA can be programmed in two ways: directly from a PC, and from an on-board Platform Flash

ROM that is also user-programmable. A jumper on the Basys board determines which source (PC or

ROM) the FPGA will use to load its configuration. Note that a demonstration configuration is loaded

into the Basys board during manufacturing. If that configuration has not been overwritten, it can be

automatically loaded into the FPGA by setting the Mode Select Jumper to “ROM”, and cycling power

or pressing the reset button (labeled “BTN_R”).

The FPGA and the Platform Flash ROM can be programmed from a PC using Digilent’s Adept

software or Xilinx’s iMPACT software (both are available for free download). Digilent’s JTAG3 cable

can be used to connect the board to a PC for programming with either software package.

To program the Basys board, connect the programming cable to the board

and to a PC, and apply power to the Basys board. Start the programming

software, and wait for the FPGA and the Platform Flash ROM to be

automatically identified. To program the FPGA, select the desired .bit file; to

program the Platform Flash, select the desired .mcs file. Right-click on the

device to be programmed, and select the “program” function. The

configuration file will be sent to the FPGA or Platform Flash, and the

software will indicate whether programming was successful.

Both the FPGA and Platform Flash ROM will always appear in the scan chain. After the Platform

Flash ROM has been loaded with a configuration file, the FPGA can automatically load that file at

power-on if programming mode control jumper is loaded in the ROM position.

A reset button is provided (labeled “BTN_R”) that can erase the configuration in the FPGA, and start a

new programming cycle. An LED labeled “LD_D” will illuminate whenever the FPGA has been

successfully configured.