Pin definitions – Cypress CY7C0430BV User Manual

Page 7

CY7C0430BV

CY7C0430CV

Document #: 38-06027 Rev. *B

Page 7 of 37

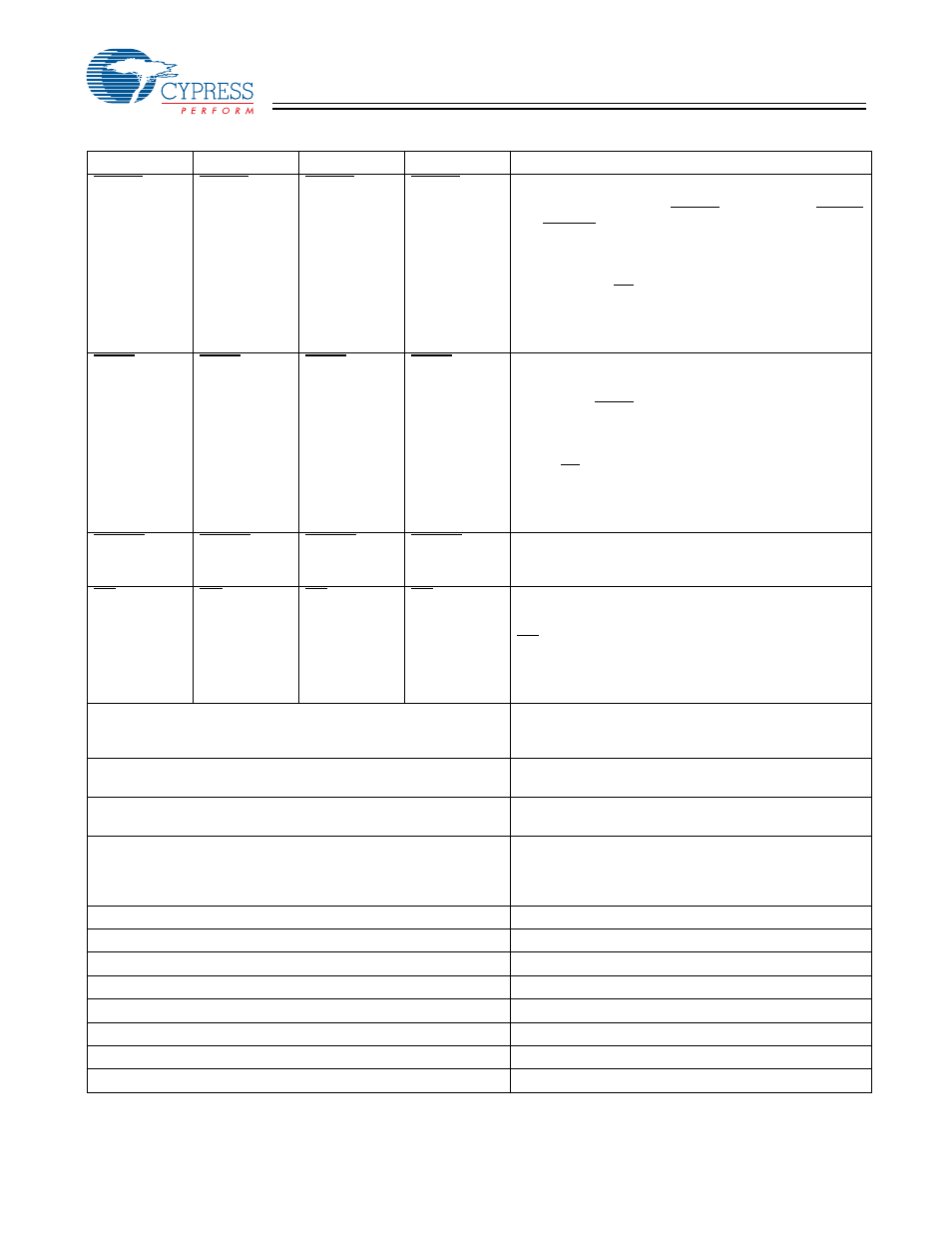

CNTRD

P1

CNTRD

P2

CNTRD

P3

CNTRD

P4

Counter Readback Input. When asserted LOW, the

internal address value of the counter will be read back on

the address lines. During CNTRD operation, both CNTLD

and CNTINC must be HIGH. Counter readback operation

has higher priority over mask register readback operation.

Counter readback operation is independent of port chip

enables. If address readback operation occurs with chip

enables active (CE

0

= LOW, CE

1

= HIGH), the data lines

(I/Os) will be three-stated. The readback timing will be

valid after one no-operation cycle plus t

CD2

from the rising

edge of the next cycle.

MKRD

P1

MKRD

P2

MKRD

P3

MKRD

P4

Mask Register Readback Input. When asserted LOW,

the value of the mask register will be readback on address

lines. During mask register readback operation, all

counter and MKLD inputs must be HIGH (see Counter

and Mask Register Operations truth table). Mask register

readback operation is independent of port chip enables.

If address readback operation occurs with chip enables

active (CE

0

= LOW, CE

1

= HIGH), the data lines (I/Os) will

be three-stated. The readback will be valid after one

no-operation cycle plus t

CD2

from the rising edge of the

next cycle.

CNTINT

P1

CNTINT

P2

CNTINT

P3

CNTINT

P4

Counter Interrupt Flag Output. Flag is asserted LOW

for one clock cycle when the counter wraps around to

location zero.

INTP1

INTP2

INTP3

INTP4

Interrupt Flag Output. Interrupt permits communications

between all four ports. The upper four memory locations

can be used for message passing. Example of operation:

INT

P4

is asserted LOW when another port writes to the

mailbox location of Port 4. Flag is cleared when Port 4

reads the contents of its mailbox. The same operation is

applicable to ports 1, 2, and 3.

TMS

JTAG Test Mode Select Input. It controls the advance of

JTAG TAP state machine. State machine transitions occur

on the rising edge of TCK.

TCK

JTAG Test Clock Input. This can be CLK of any port or

an external clock connected to the JTAG TAP.

TDI

JTAG Test Data Input. This is the only data input. TDI

inputs will shift data serially in to the selected register.

TDO

JTAG Test Data Output. This is the only data output.

TDO transitions occur on the falling edge of TCK. TDO

normally three-stated except when captured data is

shifted out of the JTAG TAP.

CLKBIST

BIST Clock Input.

GND

Thermal Ground for Heat Dissipation.

V

SS

Ground Input.

V

DD

Power Input.

V

SS1

Address Lines Ground Input.

V

DD1

Address Lines Power Input.

V

SS2

Data Lines Ground Input.

V

DD2

Data Lines Power Input.

Pin Definitions

(continued)

Port 1

Port 2

Port 3

Port 4

Description