Cypress CY7C0430BV User Manual

Page 22

CY7C0430BV

CY7C0430CV

Document #: 38-06027 Rev. *B

Page 22 of 37

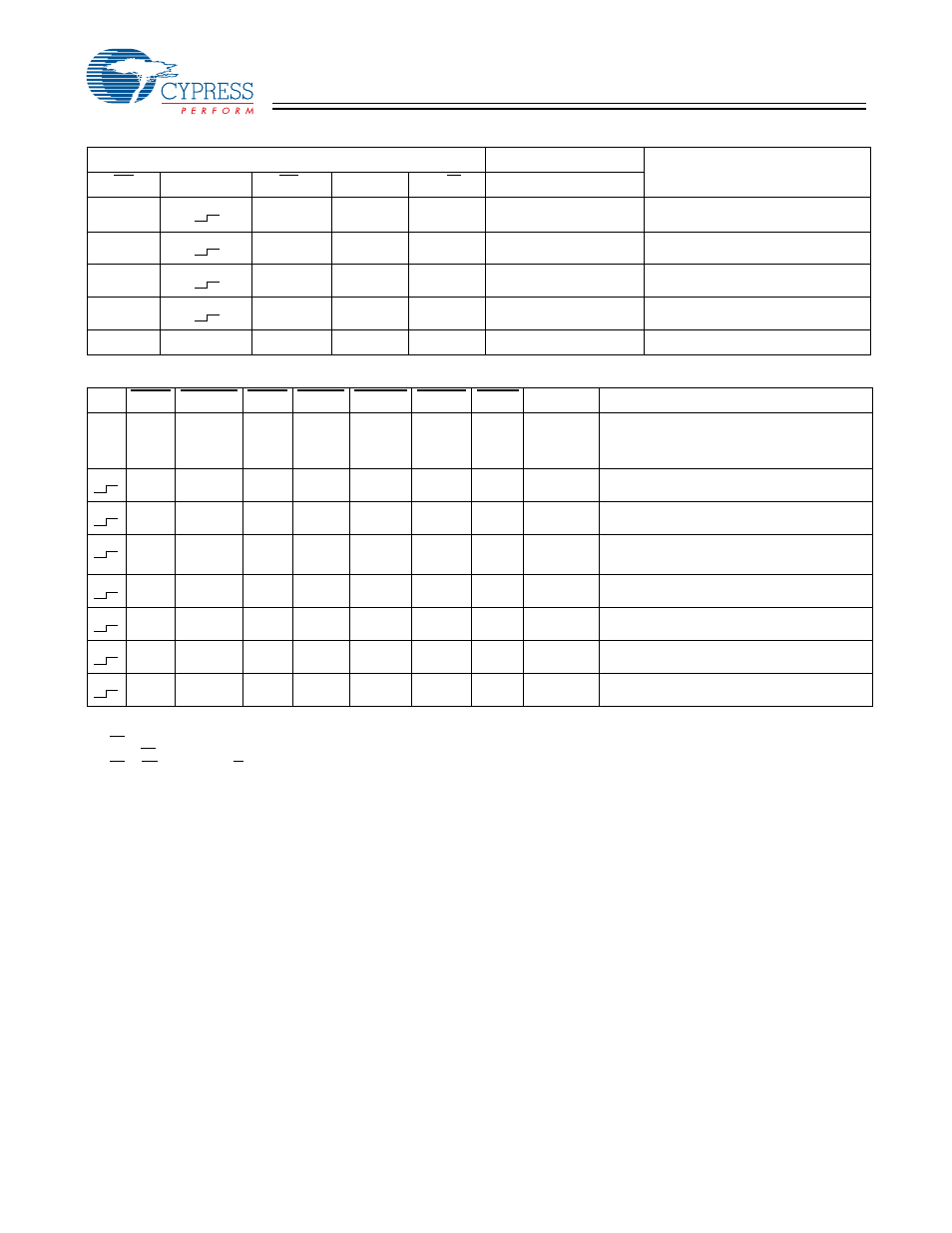

Table 1. Read/Write and Enable Operation

(Any Port)

[45, 46, 47]

Inputs

Outputs

Operation

OE

CLK

CE

0

CE

1

R/W

I/O

0

–I/O

17

X

H

X

X

High-Z

Deselected

X

X

L

X

High-Z

Deselected

X

L

H

L

D

IN

Write

L

L

H

H

D

OUT

Read

H

X

L

H

X

High-Z

Outputs Disabled

Table 2. Address Counter and Counter-Mask Register Control Operation (Any Port)

[45, 48, 49]

CLK MRST CNTRST MKLD CNTLD CNTINC CNTRD MKRD

Mode

Operation

X

L

X

X

X

X

X

X

Master-

Reset

Counter/Address Register Reset and Mask

Register Set (resets entire chip as per reset

state table)

H

L

X

X

X

X

X

Reset

Counter/Address Register Reset

H

H

L

X

X

X

X

Load

Load of Address Lines into Mask Register

H

H

H

L

X

X

X

Load

Load of Address Lines into Counter/Address

Register

H

H

H

H

L

X

X

Increment Counter Increment

H

H

H

H

H

L

X

Readback Readback Counter on Address Lines

H

H

H

H

H

H

L

Readback Readback Mask Register on Address Lines

H

H

H

H

H

H

H

Hold

Counter Hold

Notes:

45. “X” = “Don’t Care,” “H” = V

IH

, “L” = V

IL

.

46. OE is an asynchronous input signal.

47. When CE changes state, deselection and read happen after one cycle of latency.

48. CE

0

= OE = V

IL

; CE

1

= R/W = V

IH

.

49. Counter operation and mask register operation are independent of Chip Enables.