Cypress CY7C0430BV User Manual

Page 2

CY7C0430BV

CY7C0430CV

Document #: 38-06027 Rev. *B

Page 2 of 37

Functional Description

The Quadport Datapath Switching Element (DSE) family offers

four ports that may be clocked at independent frequencies

from one another. Each port can read or write up to 133 MHz

[1]

,

giving the device up to 10 Gb/s of data throughput. The device

is 1-Mb (64K × 18) in density. Simultaneous reads are allowed

for accesses to the same address location; however, simulta-

neous reading and writing to the same address is not allowed.

Any port can write to a certain location while other ports are

reading that location simultaneously, if the timing spec for port

to port delay (t

CCS

) is met. The result of writing to the same

location by more than one port at the same time is undefined.

Data is registered for decreased cycle time. Clock to data valid

t

CD2

= 4.2 ns. Each port contains a burst counter on the input

address register. After externally loading the counter with the

initial address the counter will self-increment the address inter-

nally (more details to follow). The internal write pulse width is

independent of the duration of the R/W input signal. The

internal write pulse is self-timed to allow the shortest possible

cycle times.

A HIGH on CE

0

or LOW on CE

1

for one clock cycle will power

down the internal circuitry to reduce the static power

consumption. One cycle is required with chip enables asserted

to reactivate the outputs.

The CY7C0430BV and CY7C0430CV (64K × 18 device)

supports burst contains for simple array partitioning. Counter

enable inputs are provided to stall the operation of the address

input and utilize the internal address generated by the internal

counter for fast interleaved memory applications. A port’s burst

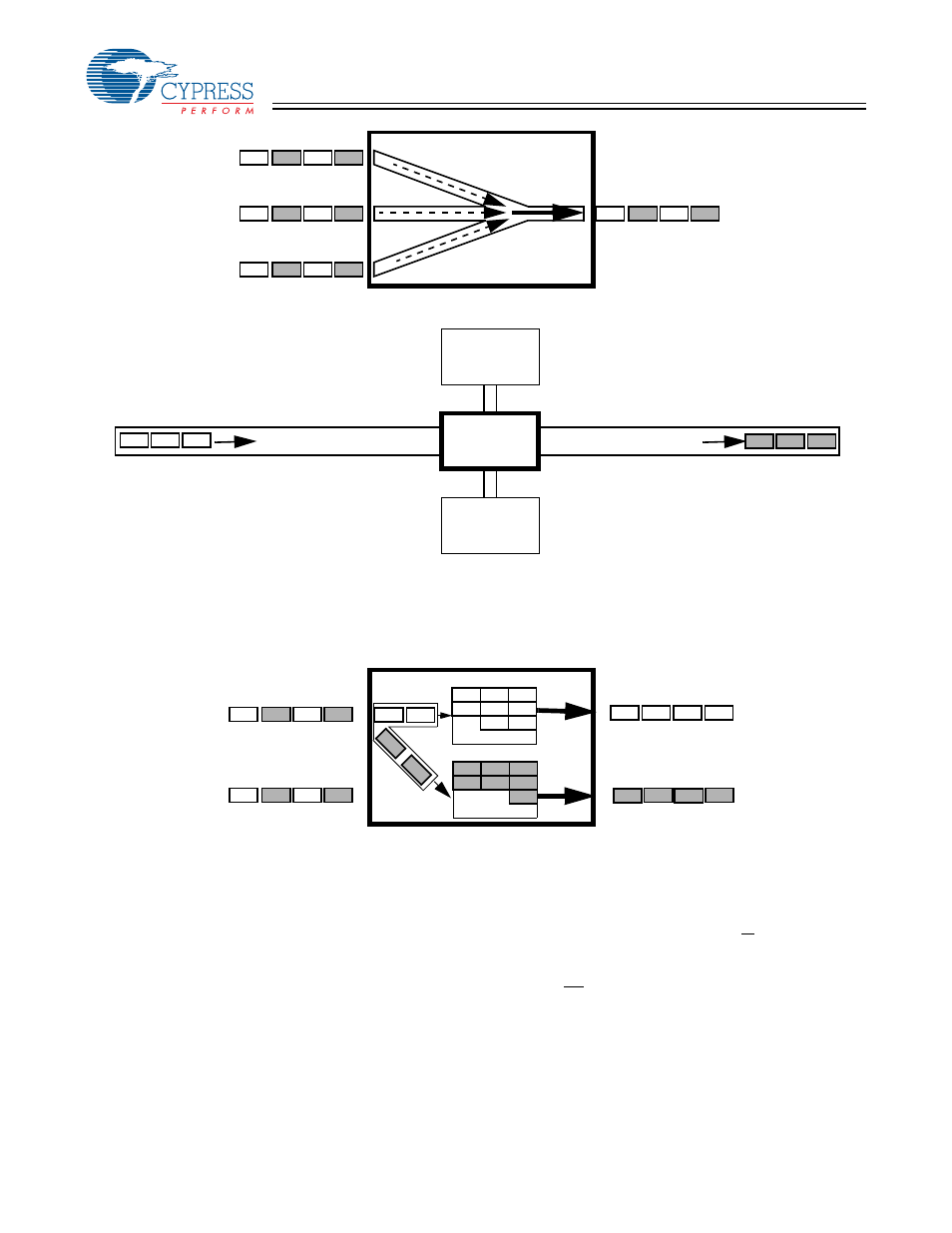

DATA PATH AGGREGATOR

PORT 1

PORT 2

PORT 3

PORT 4

DATA PATH MANAGER FOR

PARALLEL PACKET PROCESSING

Processor 2

Processor 1

Pre-processed DATA Path

Processed DATA Path

DATA CLASSIFICATION ENGINE

PORT 2

PORT 4

PORT 1

PORT 3

Queue #1

Queue #2

QuadPort

DSE Family