15 gigabit ethernet controller (gbe) interface, Figure 6 gbe controller implementation, Gigabit ethernet controller (gbe) interface – Kontron SMARC-sAT30 User Manual

Page 33

User’s Guide

33

E

D

GE

F

IN

G

E

R

(J3)

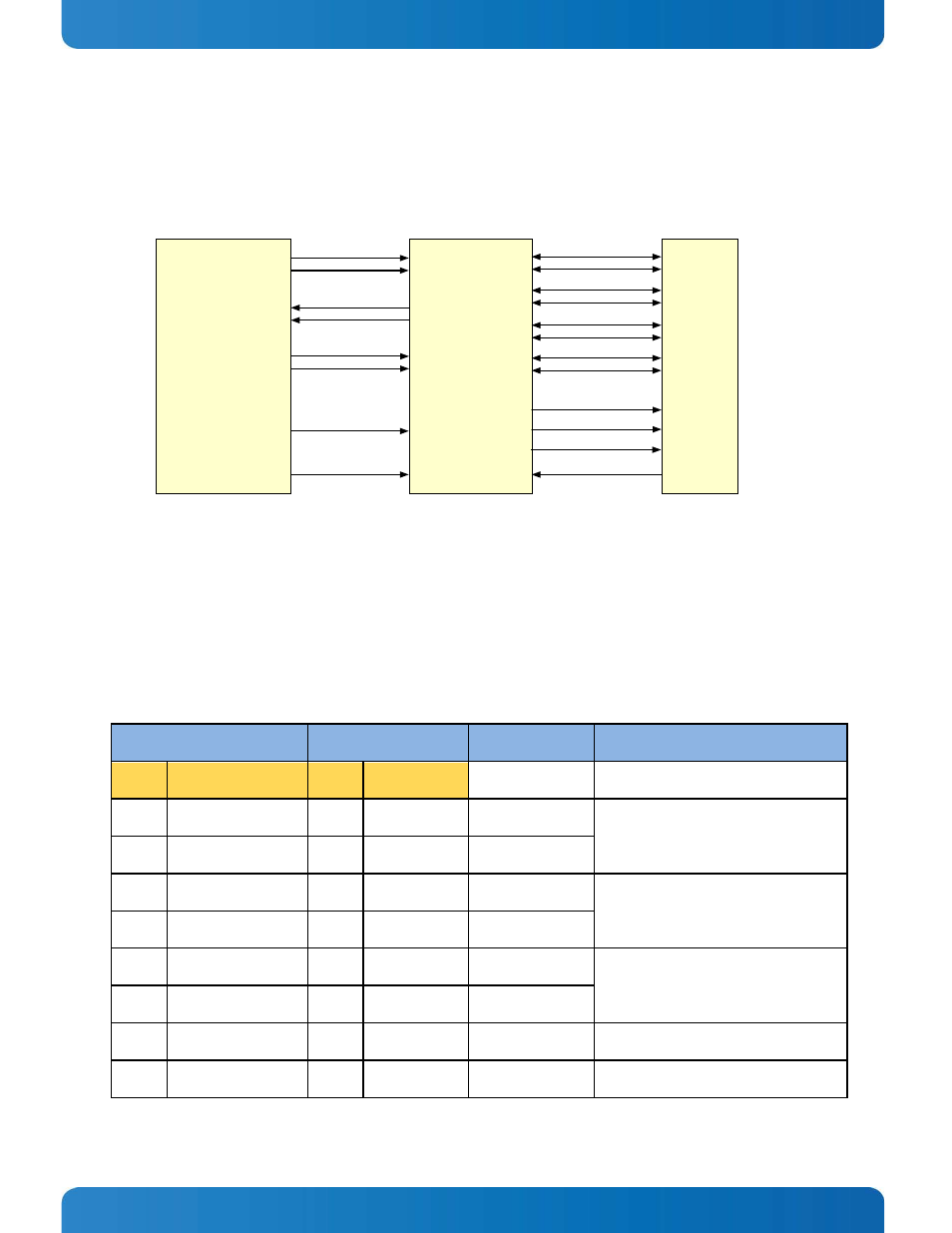

3.2.15 Gigabit Ethernet Controller (GbE) Interface

The SMARC sAT30 module supports one GbE interface. This is accomplished by using the Intel I210 (Springville) GbE

MAC+PHY using one of the T30 SoC’s PCIe interfaces. This is diagrammed below. The PCIe coupling caps are not shown

in the diagram.

AH25

AJ25

AG23

AG22

GBE_PCIE_TX_P

24

GBE_PCIE_TX_N

23

GBE_PCIE_RX_P

21

GBE_PCIE_RX_N

20

GBE_PCIE_CLK_P

GBE

58

GBE_MDI0_P

57

GBE_MDI0_N

55

GBE_MDI1_P

GBE_MDI1_N

54

53

GBE_MDI2_P

52

GBE_MDI2_N

GBE_MDI3_P

P30

P29

P27

P26

P24

P23

T30 CPU

(U10)

AJ27

AH27

GBE_PCIE_CLK_N

26 CONTROLLER 50

25 INTEL I210 49

(U27)

GBE_MDI3_N

P20

P19

AG25

GBE_PCIE_RST#

17

31

GBE_LINK100#

33

GBE_LINK1000#

30

GBE_LINK_ACT#

P21

P22

P25

J2

GBE_PCIE_DIS#

61

16

PCIE_WAKE#

S146

Figure 6 GbE Controller Implementation

The following table details the Tegra to I210 connection details.

NVIDIA T30 CPU

Intel I210

Net Name

Notes

Pin #

Pin Name

Pin #

Pin Name

AH25

PEX_L5_TXP

24

PE_RX+

GbE_PCIE_TX_P

Differential PCIe GbE transmit data

pair

AJ25

PEX_L5_TXN

23

PE_RX-

GbE_PCIE_TX_N

AG23

PEX_L5_RXP

21

PE_TX+

GbE_PCIE_RX_P

Differential PCIe GbE receive data pair

AG22

PEX_L5_RXN

20

PE_TX-

GbE_PCIE_RX_N

AJ27

PEX_CLK3P

26

PECLK+

GbE_PCIE_CLK_P

Differential PCIe GbE reference clock

AH27

PEX_CLK3N

25

PECLK-

GbE_PCIE_CLK_N

AG25

PEX_L2_RST#

17

PE_RST#

GbE_PCIE_RST#

PCIe GbE reset input

J2

GMI_AD14

61

SDP1

GbE_PCIE_DIS#

INTEL I210 PCIe interface disable