13 pcie interfaces, Pcie interfaces – Kontron SMARC-sAT30 User Manual

Page 30

User’s Guide

30

3.2.13 PCIe Interfaces

The SMARC sAT30 module supports two external PCIe x 1 interfaces, designated PCIE_A and PCIE_B in the SMARC

specification. Of the three the NVIDIA T30 CPU PCIe interfaces, one is used on the Module for the GbE controller,

described in Section 3.2.13 Gigabit Ethernet Controller (GbE) Interface. Two are used for SMARC external PCIe

interfaces.

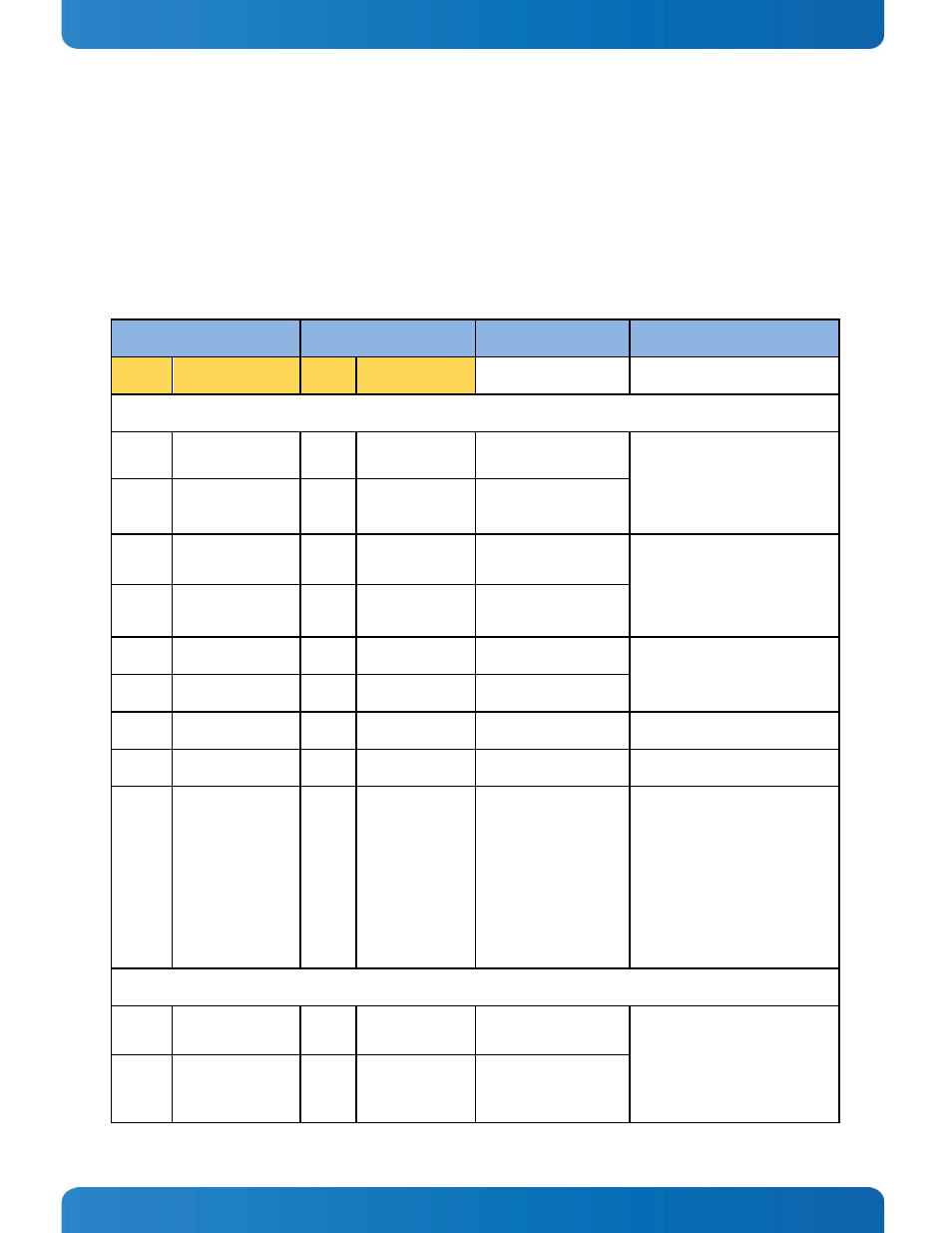

PCIe interface signals are exposed on the SMARC sAT30 edge connector as shown below:

SMARC sAT30 Edge Finger

NVIDIA T30 CPU

Net Name

Notes

Pin #

Pin Name

Pin #

Pin Name

PCIe_Link A

P89

PCIE_A_TX+

AF21

PEX_L4_TXP

PCIEA_TX_P

Differential PCIe Link A

transmit data pair 0. Series

decoupling caps are provided

in the Module.

P90

PCIE_A_TX-

AG21

PEX_L4_TXN

PCIEA_TX_N

P86

PCIE_A_RX+

AH24

PEX_L4_RXP

PCIEA_RX_P

Differential PCIe Link A receive

data pair 0. Series coupling

caps are not provided in the

Module.

P87

PCIE_A_RX-

AJ24

PEX_L4_RXN

PCIEA_RX_N

P83

PCIE_A_REFCK+

AB23

PEX_CLK2P

PCIEA_REF_CLK_P

Differential PCIe Link A

reference clock output

P84

PCIE_A_REFCK-

AB24

PEX_CLK2N

PCIEA_REF_CLK_N

P78

PCIE_A_CKREQ#

AD26

PEX_L1_CLKREQ

PCIEA_CLK_REQ#

PCIe Port A clock request input

P74

PCIE_A_PRSNT#

AD24

PEX_L1_PRSNT

PCIEA_PRSNT#

PCIe Port A present input

P75

PCIE_A_RST#

AG27

PEX_L1_RST

T30_PCIEA_RST#

PCIe Port B reset output, active

low.

Provision is provided to

connect pin P75 to GMI_AD15

(F1) through a 0 ohm resistor,

R303 (R303 should not be

installed)

PCIe_Link B

S90

PCIE_B_TX+

AF18

PEX_L0_TXP

PCIEB_TX_P

Differential PCIe Link B

transmit data pair 0.

Series decoupling caps are

provided in the Module.

S91

PCIE_B_TX-

AG18

PEX_L0_TXN

PCIEB_TX_N