8 parallel lcd display interface, Figure 3: t30 module parallel lcd implementation, Parallel lcd display interface – Kontron SMARC-sAT30 User Manual

Page 18

User’s Guide

18

EDG

E

F

ING

E

R

(J3)

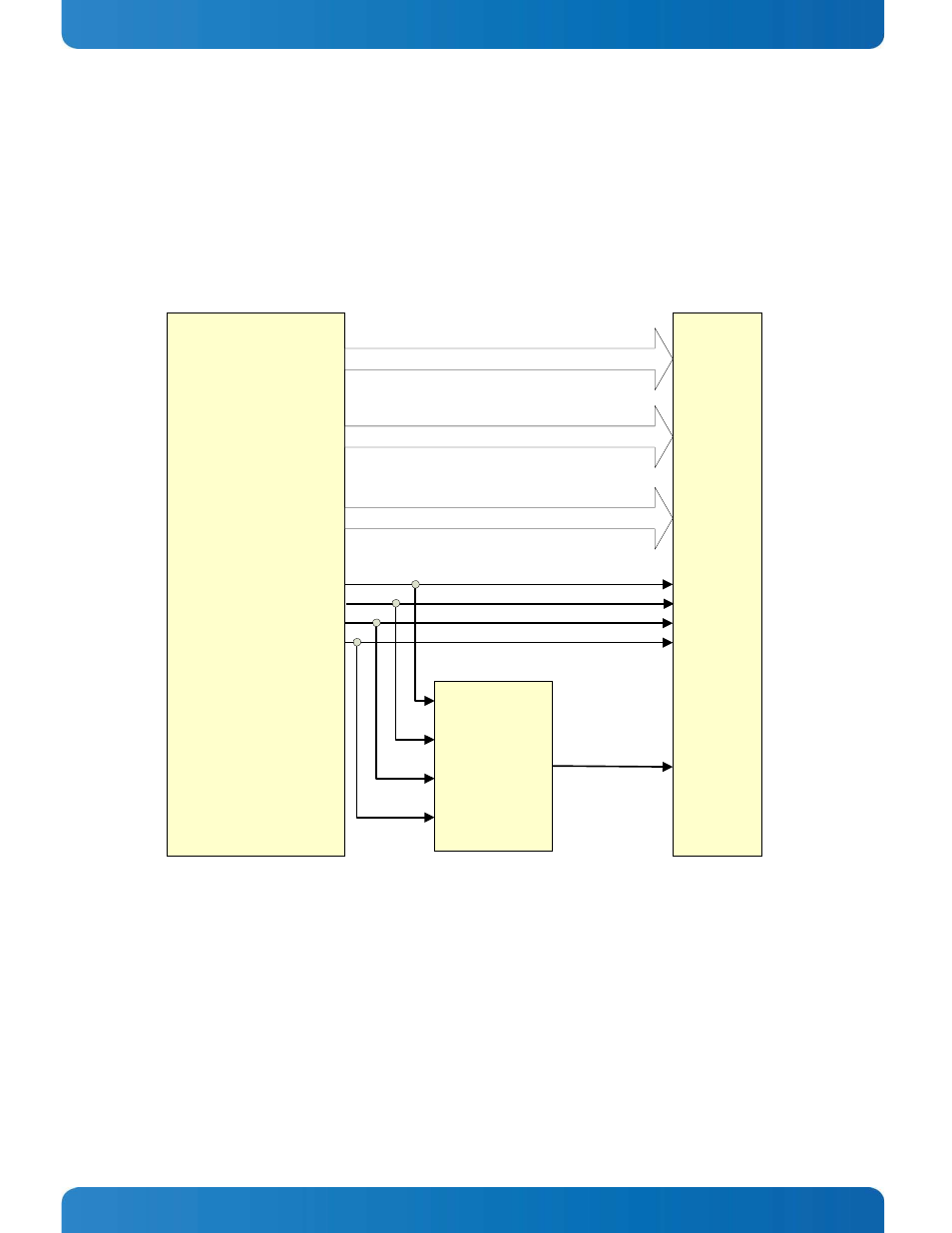

3.2.8 Parallel LCD Display Interface

The NVIDIA Tegra parallel 24 bit LCD interface is brought to the Module edge connector. The interface runs at the 1.8V

Module I/O voltage. This voltage swing may be used directly with 1.8V capable Carrier Board LVDS transmitters, such as

the TI SN75LVDS83B. The 1.8V signaling may not be suitable for direct connection to a parallel flat panel. Generally

speaking, only small panels, with screen diagonals of 5” or less, are available with a 1.8V interface. Larger parallel LCD

panels are likely to use 3.3V signaling and a set of voltage translators / buffers would be needed on the Carrier.

RED

T30_LCD_D[17:12,23,22]

GREEN

T30_LCD_D[11:6,21,20]

BLUE

T30_LCD_D[5:0,19,18]

T30 CPU

(U10)

AG9

AF16

AF10

AG11

T30_LCD_DE

T30_LCD_HSYNC

T30_LCD_VSYNC

T30_LCD_PCLK

S120

S122

S121

S123

F9

H11

G10

CPLD

(U23)

G11

T30_LCD_DPCLK

S142

F10

Figure 3: T30 Module Parallel LCD Implementation

The mapping of the NVIDIA Tegra parallel LCD balls to the SMARC edge connector is shown in the table below. Note

that the NVIDIA pin names and the SMARC pin names have different assumptions about color mappings, which can

make things confusing. Basically, NVIDIA maps the 18 bits or R, G, B for 6 bit color depth to D17:0. For NVIDIA, the

extra bits used for a 24 bit color implementation come out on NVIDIA D23:18. The SMARC has a different convention:

Red is D23:16; Blue is D15:8 and Green is D7:0. For 24 bit implementations, all bits are used. For 18 bit

implementations, in SMARC, the least significant bits (Red D17:16, Green D9:8, Blue D1:0) are dropped.