Kontron SMARC-sAT30 User Manual

Page 28

User’s Guide

28

E

D

GE

F

IN

GE

R

(J3)

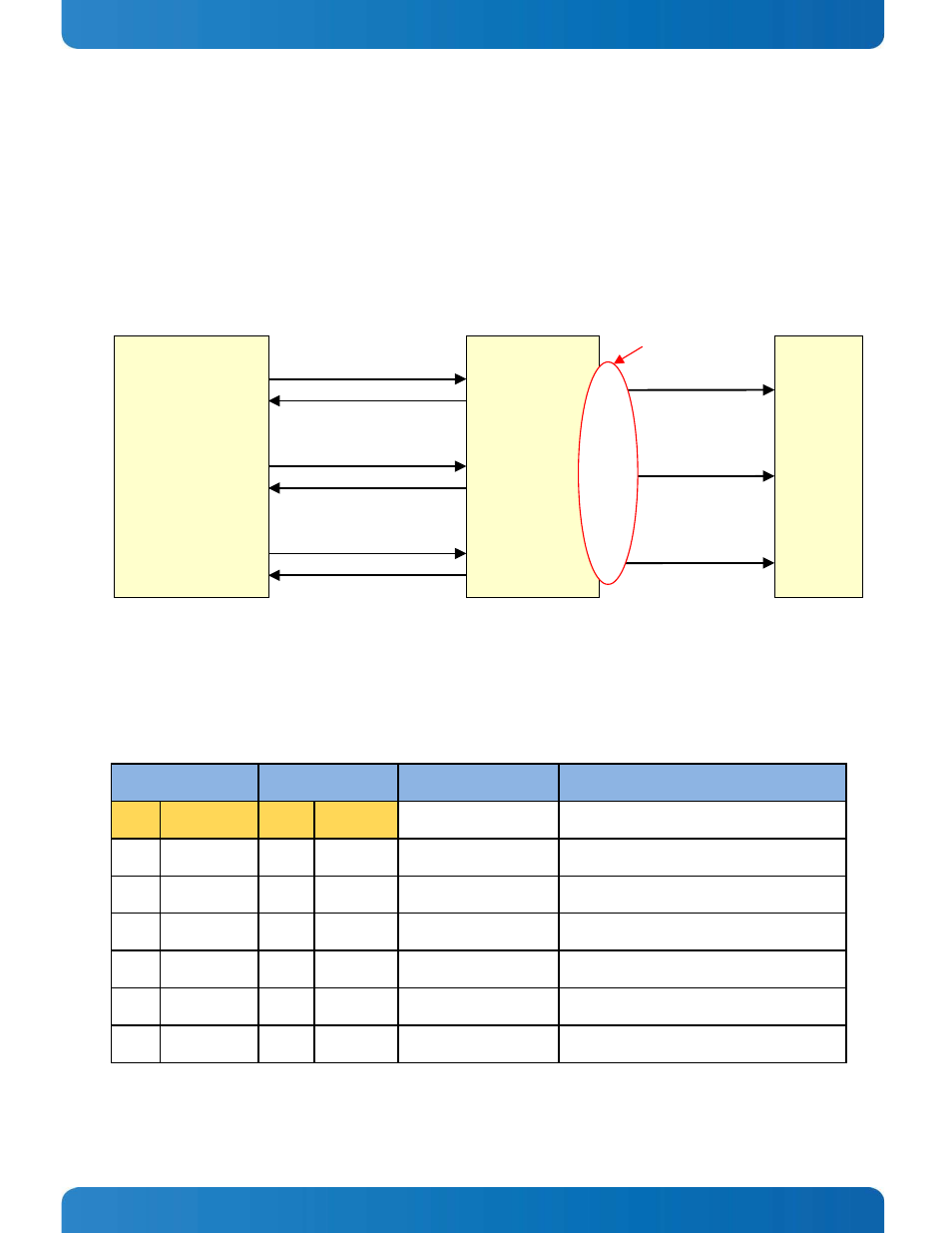

The SMARC Hardware specification defines USBx_EN_OC# (where x is 0, 1 and 2 for use with USB0, USB1 and USB2)

pins as multifunction pins to use for power enable of USBx ports, as well as for over current indication. The SMARC

sAT30 complies with this definition. These nets are provided with pull up resistors on the Module. The Module CPLD

contains the glue logic required for this implementation.

The sAT30 Module USB power enable and over current indication logic implementation is shown in the following block

diagram. There are 10K pull-up resistors on the Module on the SMARC USBx_EN_OC# lines. The CPLD outputs driving

the USBx_EN_OC# lines are open-drain. The Carrier board USB power switch, if present, is enabled by virtue of the 10K

Module pull-up to 3.3V.

EN_USB0_VBUS_CPLD

D6

H2

F4

USB0_OC_CPLD

L4

10K Pull-Ups to 3.3V

On Module

L9

USB0_EN_OC#

P62

T30 CPU

(U10)

EN_USB1_VBUS_CPLD

J5

L1

K7

USB1_OC_CPLD

L5

EN_USB2_VBUS_CPLD

J7

L2

F6

USB2_OC_CPLD

L3

CPLD

(U23)

K9

L10

USB1_EN_OC#

USB2_EN_OC#

P67

P71

Figure 4: External USB Port Power Distribution Logic Implementation

USB port power enable and over current logic implementation between the T30 CPU and CPLD is shown in the following

table:

NVIDIA T30 CPU

CPLD

Net Name

Notes

Pin #

Pin Name

Pin #

Pin Name

D6

GMI_CS4#

H2

IO_H2

EN_USB0_VBUS_CPLD

USB Port0 power enable

J5

GMI_CS6#

L1

IO_L1

EN_USB1_VBUS_CPLD

USB Port1 power enable

J7

GMI_CS7#

L2

IO_L2

EN_USB2_VBUS_CPLD

USB Port2 power enable

F4

GMI_AD09

L4

IO_L4

USB0_OC_CPLD#

USB Port0 over current indication signal

K7

GMI_CS1#

L5

IO_L5

USB1_OC_CPLD#

USB Port1 over current indication signal

F6

GMI_CS2#

L3

IO_L3

USB2_OC_CPLD#

USB Port2 over current indication signal