14 lpc bus interface, Lpc bus interface, Table 11: lpc addresses – Kontron COMe-cOHXX User Manual

Page 48

Kontron COMe-cOH2/COMe-cOH6 User’s Guide

www.kontron.com

43

with the COM Express Rev 2.0 specification. Carrier Board SPI boot support is

new with COM Express Rev 2.0. For additional implementation information,

refer to the PICMG COM Express® Design Guide on the PICMG website

4.1.14

LPC Bus Interface

The Low Pin Count (LPC) interface signals are connected to the AMD Fusion

Controller Hub. The LPC low-speed interface can be used for peripheral

circuits. For example, it can be used as an external super I/O controller to

combine legacy-device support into a single IC. The implementation of this

subsystem complies with the COM Express

TM

specification. For additional

implementation information, refer to the PICMG COM Express® Design Guide on

the PICMG website.

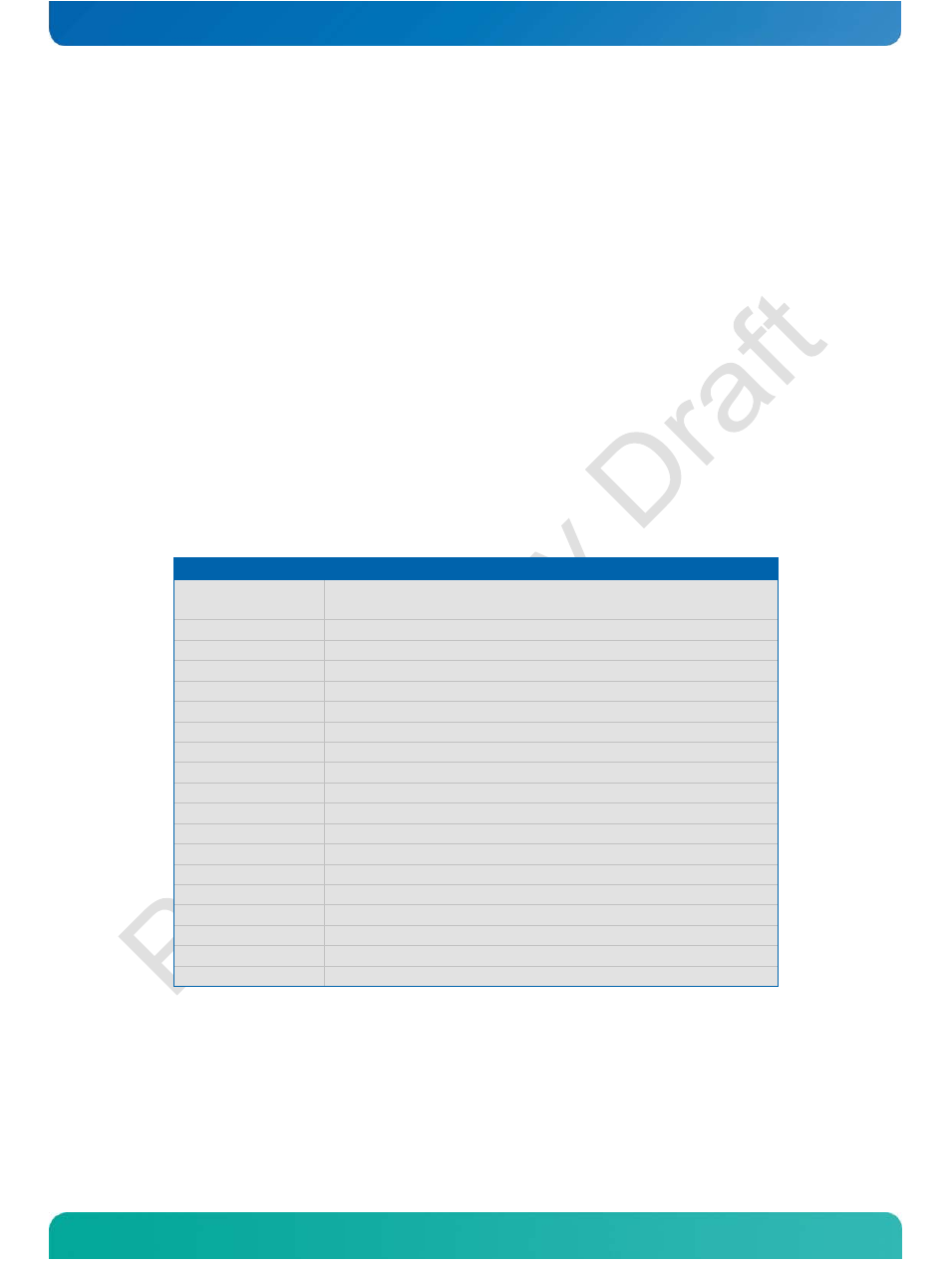

Table 11: LPC Addresses

Address (HEX)

Device

0000 - 00FF

IBM PC compatible devices (IRQ-Controller,

Keyboard, RTC, etc.)

002E-002F

Optional: Super I/O W83627

004e - 004f

TPM

01F0 - 01F7

Fixed Disk

03C0 - 03CF

VGA/EGA compatible registers

03F6

Fixed Disk

0400 - 043F

SMBus

0480 - 04BF

GPIO ICH

04D0 - 04D1

IRQ Configuration

08F0 - 08FF

Optional

0900 - 091F

Power Management

0A80 - 0A83

Reserved

0CF8 - 0CFF

PCI Configuration

D880 - D887

PCI LAN Controller *

E080 - E09F

PCI USB Controller *

E480 - E49F

PCI USB Controller *

E880 - E887

PCI VGA Controller *

EF00 - EF1F

PCI USB Controller*

FFA0 – FFAF

PCI IDE Controller *

* = not fixed, configured by the BIOS automatically and may be

different in other system configurations.