18 delay timer control/status register - 15, Vmp3 configuration – Kontron VMP3 User Manual

Page 75

VMP3

Configuration

ID 29230, Rev. 01

© 2005 Kontron Modular Computers GmbH

Page 4 - 15

29230

.01.UG.VC.050727/091436

P R E L I M I N A R Y

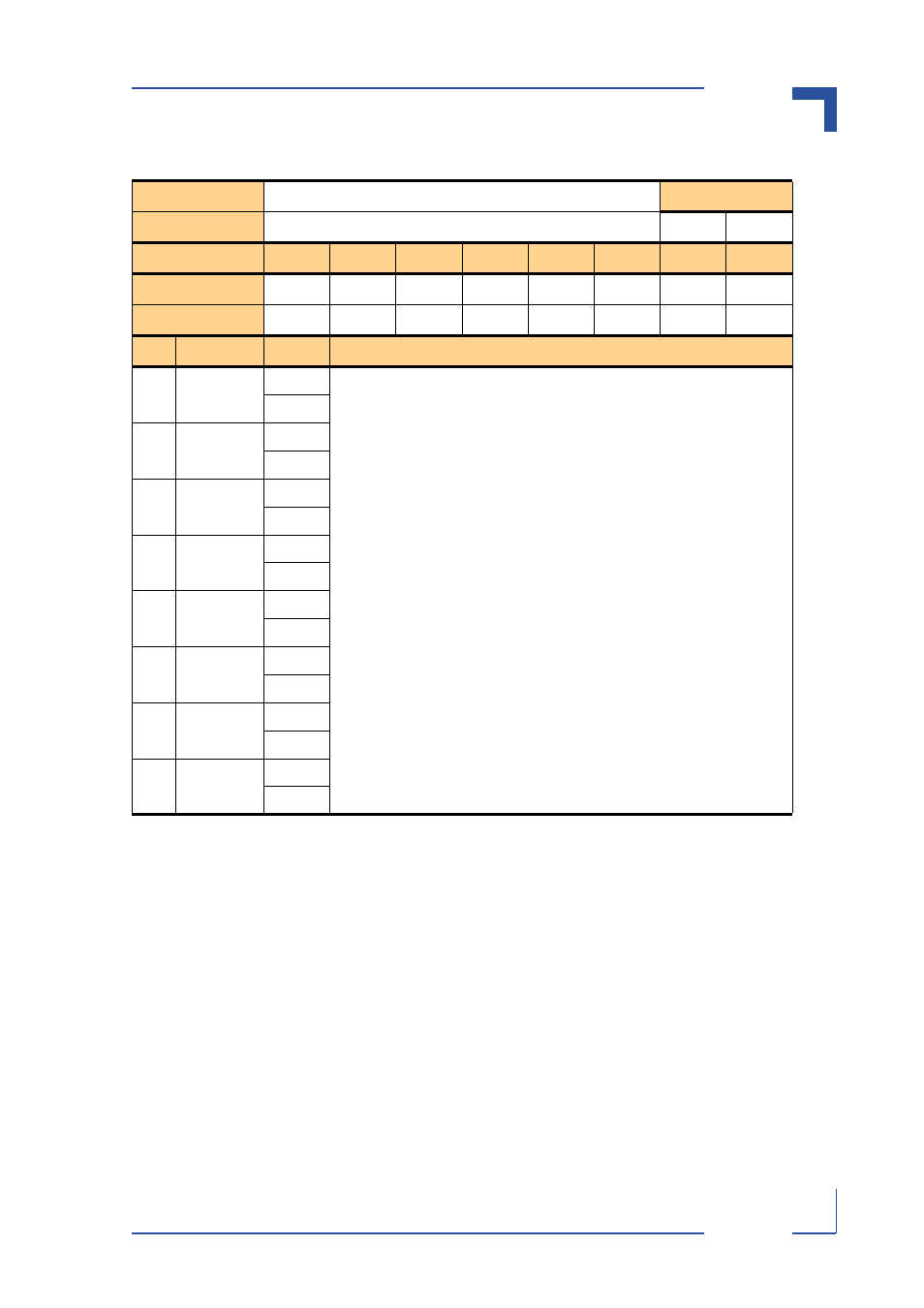

Table 4-18: Delay Timer Control/Status Register

REGISTER NAME

DELAY TIMER CONTROL/STATUS REGISTER

ACCESS

ADDRESS

0xFFFF A014

R

W

BIT POSITION

MSB

7

6

5

4

3

2

1

0

LSB

CONTENT

DTC7

DTC6

DTC5

DTC4

DTC3

DTC2

DTC1

DTC0

DEFAULT

0

0

0

0

0

0

0

0

BIT CONTENT STATE

DESCRIPTION

0

DTC0

0

The hardware delay timer is operated via one simple 8-bit control/status

register. The following table indicates 1) the possible timing intervals pro-

vided, and 2) when read, the time elapsed since the last trigger/reset of the

timer.

DTC[7:0] Value

Accuracy

Bit 0:

1 µs

< + 40%

Bit 1:

5 µs

< + 8%

Bit 2:

10 µs

< + 4%

Bit 3:

50 µs

< + 0.8%

Bit 4:

100 µs

< + 0.4%

Bit 5:

250 µs

< + 0.16%

Bit 6:

0.5 ms

< + 0.08%

Bit 7:

1 ms

< + 0.04%

1

1

DTC1

0

1

2

DTC2

0

1

3

DTC3

0

1

4

DTC4

0

1

5

DTC5

0

1

6

DTC6

0

1

7

DTC7

0

1

- CP3003-SA uEFI BIOS (72 pages)

- CP3003-SA (36 pages)

- CP3002 (38 pages)

- CP3002-RC uEFI (64 pages)

- CP-RIO3-05 (42 pages)

- CP3002-RC (30 pages)

- CP342 (52 pages)

- CP930 (46 pages)

- CP932 (52 pages)

- CP346 (72 pages)

- CP384 (66 pages)

- CP383 (74 pages)

- CP382 (58 pages)

- CP381 (60 pages)

- CP372 (64 pages)

- CP371 (60 pages)

- CP-RIO3-04S (38 pages)

- CP390 (36 pages)

- CPS3410 (9 pages)

- CPS3402 (9 pages)

- CPS3105 (9 pages)

- CPS3101 (9 pages)

- CPS3003-SA (19 pages)

- PB-SIO4 (34 pages)

- PB-SIO4A (34 pages)

- PB-DOUT8 (34 pages)

- VMOD-2 (82 pages)

- VSBC-32 (110 pages)

- VM42 (62 pages)

- Bootstrap Loader (24 pages)

- VMP1 with Netbootloader (120 pages)

- VMP1 (106 pages)

- NetBootLoader (86 pages)

- VMP2 (142 pages)

- CP-RIO6-923 (32 pages)

- CP-RIO6-923-F (32 pages)

- CP-RIO6-001 (28 pages)

- CP-RIO6-001-HD-VGA (46 pages)

- CP-RIO6-M (20 pages)

- CP-RIO6-B (28 pages)

- CP6925 (42 pages)

- CP6002 uEFI BIOS (76 pages)

- CP6002 IPMI (40 pages)

- CP6002 (42 pages)