Event register - 7, Vmp3 configuration – Kontron VMP3 User Manual

Page 67

VMP3

Configuration

ID 29230, Rev. 01

© 2005 Kontron Modular Computers GmbH

Page 4 - 7

29230

.01.UG.VC.050727/091435

P R E L I M I N A R Y

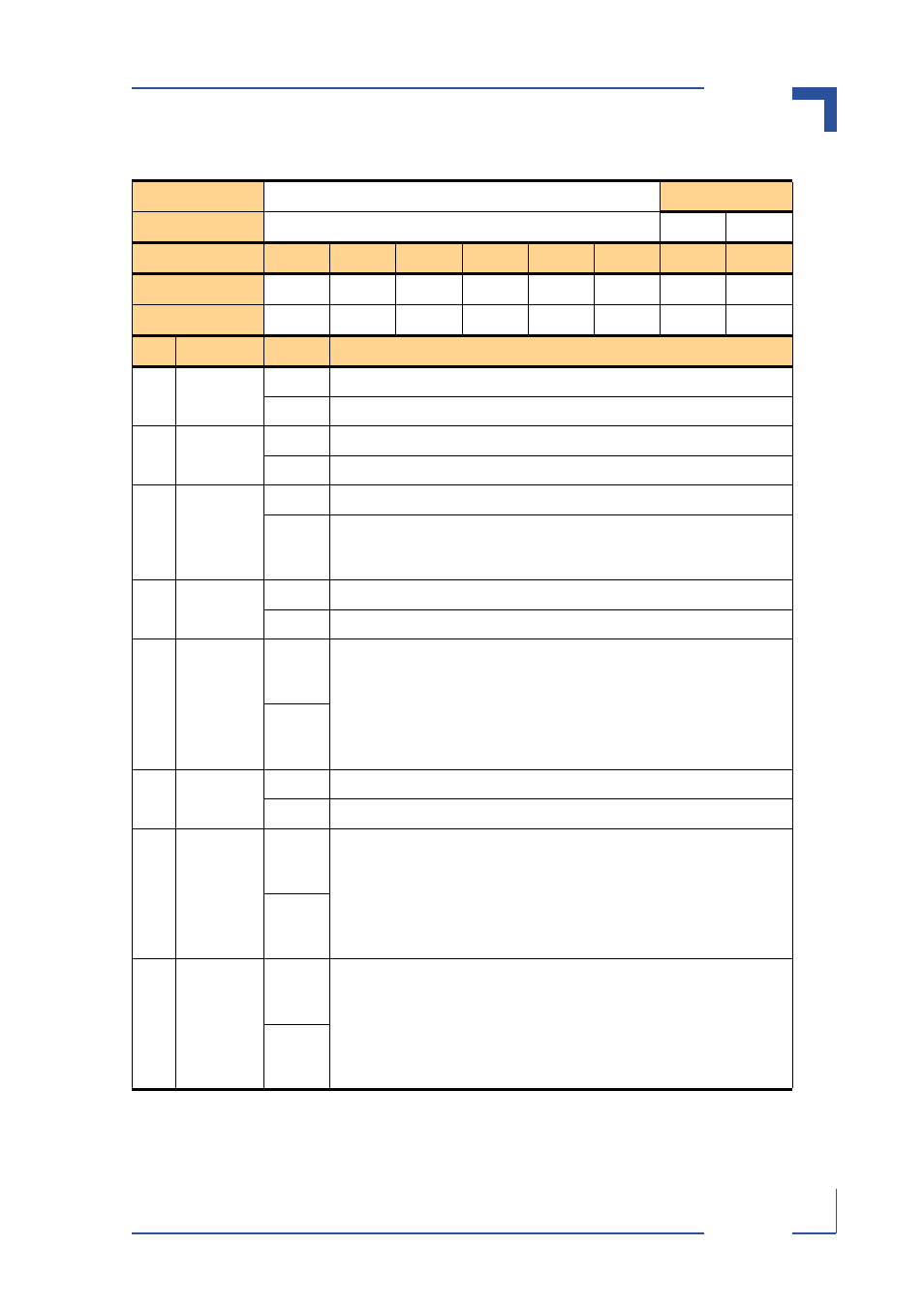

Table 4-6: Event Register

REGISTER NAME

EVENT

ACCESS

ADDRESS

0xFFFF A004

R

W

BIT POSITION

MSB

7

6

5

4

3

2

1

0

LSB

CONTENT

MC5

MC3

res.

MC2

MC8

MC1

ALARM

res.

DEFAULT

n/a

n/a

n/a

n/a

n/a

0

0

n/a

BIT CONTENT STATE

DESCRIPTION

0

reserved

0

1

1

ALARM

0

Indicates that ALARM signal on RTC has not been asserted

1

Indicates that ALARM signal on RTC has been asserted

2

MC1

0

Indicates that the MC1 signal has not been asserted

1

Indicates that the MC1 signal has been asserted

(This will result in a NMI being generated which can be cleared by writing a

’1’.)

3

MC8

0

Indicates that the EB405 is being operated in Agent mode

1

Indicates that the EB405 is being operated in Master mode

4

MC2

0

Case: MC2_INT_EN = 0

Indicates the status of the MC2 input: electrical: low = 0, high = 1

Case: MC2_INT_EN = 1 (default = 0)

The falling edge of the signal on MC2 pin sets this bit to ’1’ and generates

the MCInt on the CPU provided it is enabled there

(This may be cleared by writing a ’1’.)

1

5

reserved

0

1

6

MC3

0

Case: MC3_INT_EN = 0

Indicates the status of the MC3 input: electrical: low = 0, high = 1

Case: MC3_INT_EN = 1 (default = 0)

The falling edge of the signal on MC3 pin sets this bit to ’1’ and generates

the MCInt on the CPU provided it is enabled there

(This may be cleared by writing a ’1’.)

1

7

MC5

0

Case: MC3_INT_EN = 0

Indicates the status of the MC3 input: electrical: low = 0, high = 1

Case: MC3_INT_EN = 1 (default = 0)

The falling edge of the signal on MC3 pin sets this bit to ’1’ and generates

the MCInt on the CPU provided it is enabled there

(This may be cleared by writing a ’1’.)

1