3 memory configuration register, Memory configuration register - 5, Vmp3 configuration – Kontron VMP3 User Manual

Page 65

VMP3

Configuration

ID 29230, Rev. 01

© 2005 Kontron Modular Computers GmbH

Page 4 - 5

29230

.01.UG.VC.050727/091435

P R E L I M I N A R Y

4.2.3

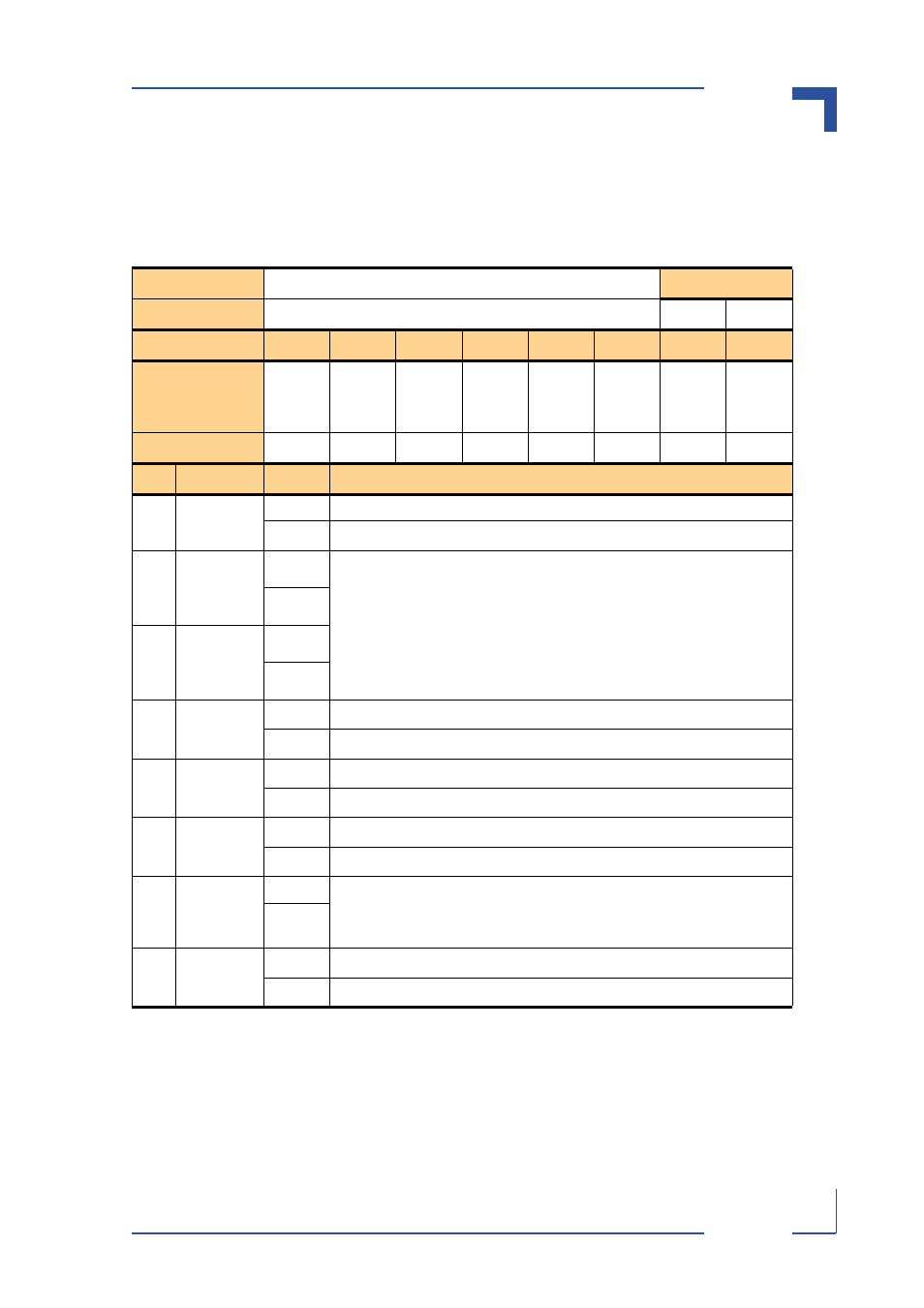

Memory Configuration Register

The memory configuration register provides information concerning SDRAM size, ECC, and

memory bus clock.

Table 4-4: Memory Configuration Register

REGISTER NAME

MEMORY CONFIGURATION

ACCESS

ADDRESS

0xFFFF A002

R

W

BIT POSITION

MSB

7

6

5

4

3

2

1

0

LS

B

CONTENT

res.

SYS_

CLK

MEM

BUS

CLOCK

ECC

res.

MEM_

SZ1

MEM_

SZ0

res.

DEFAULT

n/a

0

1

0

n/a

n/a

n/a

n/a

BIT CONTENT STATE

DESCRIPTION

0

reserved

0

1

1

MEM_SZ0

0

Memory size:

Bit 2 Bit 1

0

0

128 MB (256 Mbit chips)

0

1

256 MB (512 Mbit chips)

1

0

512 MB (1 Gbit chips)

1

1

reserved

1

2

MEM_SZ1

0

1

3

reserved

0

1

4

ECC

0

ECC not available

1

ECC available

5

MEM BUS

CLOCK

0

264 MHz (Maximum possible memory bus clock)

1

330 MHz (Maximum possible memory bus clock)

6

SYS_CLK

0

0 = 33 MHz; 1 = 66 MHz

This information is required in order to configure the PLL settings inside

the SOC.

1

7

reserved

0

1