Dll specs and operation – Achronix Speedster22i Memory PHY User Manual

Page 17

UG043, April 26, 2014

17

DLL Specs and Operation

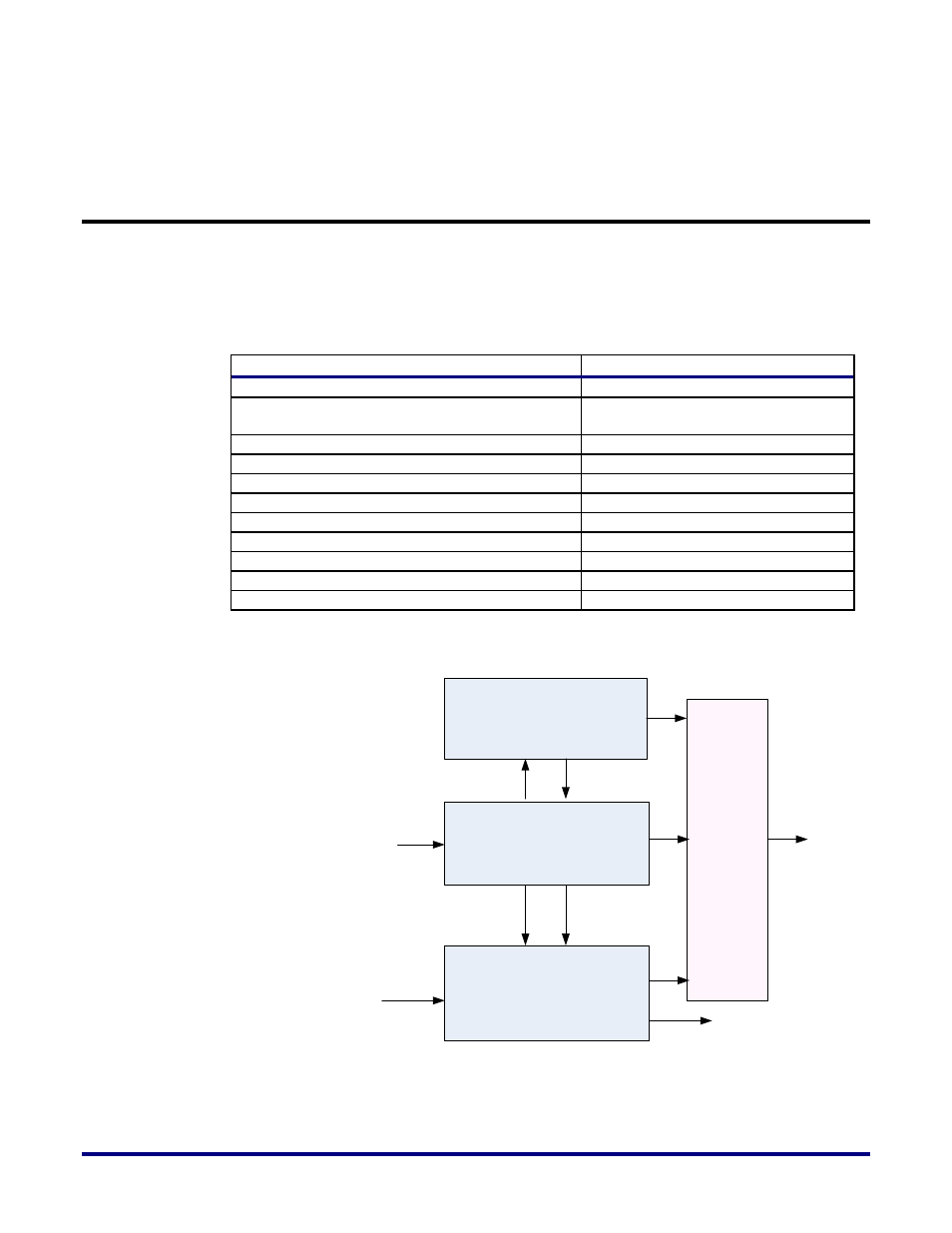

The DLL IP block in the Speedster22i HD1000 is wide range DLL with 1 Master DLL (MDLL)

and 12 Slave DLLs (SDLLs). Table 5 provides the DLL IP Specs and Figure 10 provides a

high-level block diagram of the DLL architecture.

Table 5: DLL IP Specs

Performance Parameters

Data

Frequency Range

311MHz

– 1066 MHz

Max P2P period jitter @ 2133MHz with noise

freq = 200Mhz and +/-15mV sinusoidal noise

<2% of cycle time

Minimum high low slave pulse width

25% reference cycle

DLL Lock time

< 500 reference clock cycles

SDLL Step size

360/64 degrees nominal

Output phase accuracy

+/- 4% reference clock cycle

Output phase resolution

6 bits

Slave delay adjustment

0% to 100% of reference cycle

Number of outputs per lane

1

Number of lanes per master

12

Reference Input Duty Cycle

40% - 60%

Master DLL

Slave DLL

Lock Detector

Startup Timer

View

Block

Pbias

Nbias

input reference

CLK

data_in<11:0>

sdll_out<11:0>

pin out

Figure 10: DLL Architecture High-Level Block Diagram