Cpu speedster22ihd – Achronix Speedster22i Configuration User Manual

Page 9

UG033, December 18, 2013

9

CPU

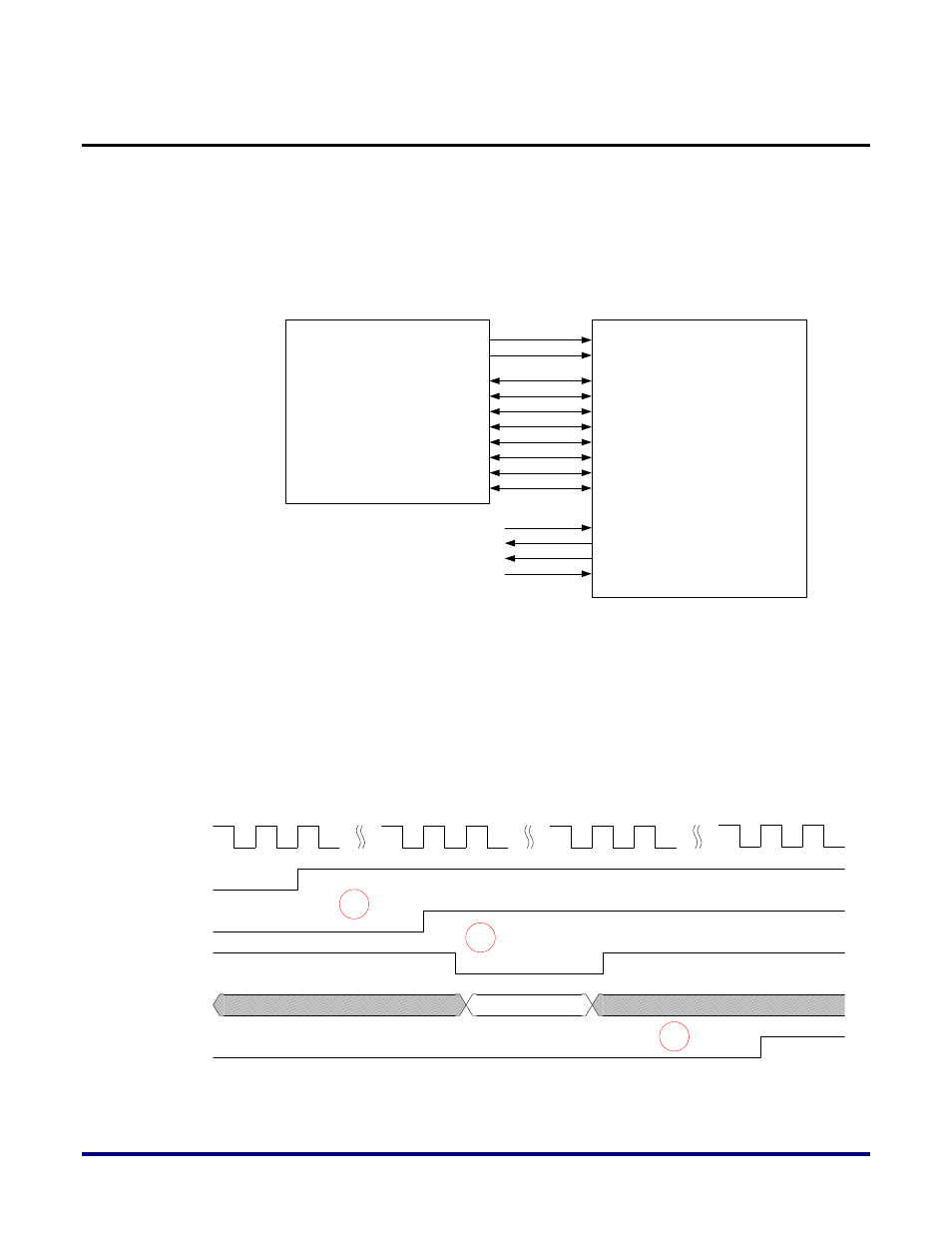

In CPU mode, an external CPU acts as the master and controls the programming operations

for the FPGA. CPU mode is an 8-bit parallel interface, clocked using CPU_CLK, with chip

select support to indicate valid data. This is generally the fastest programming mode as it

provides for the widest data width interface and a maximum supported clock rate of 25MHz.

Figure 3 below provides a block diagram of how the external CPU would be hooked up to

Speedster22iHD FPGA.

config_rstn

config_done

config_status

config_modesel[2:0]

Tied to 3'b100 for CPU mode

CSN[2]

DQ[7]

CSN[3]

DQ[6]

HOLDN

DQ[5]

SDO[0]

DQ[4]

SDO[1]

DQ[3]

SDO[2]

DQ[2]

SDO[3]

DQ[1]

SDI

DQ[0]

CSN[0]

CSN

CPU_CLK

CLK

CPU

Speedster22iHD

Figure 3: External CPU Connectivity to Speedster22iHD FPGA

As described in the Power-Up and Configuration Sequence section, the configuration mode

specific operations occur between the release of CONFIG_STATUS (indicating that the

configuration memory has been cleared and that the FPGA is ready to accept bitstream data)

and the assertion of CONFIG_DONE (stating completion of configuration). The waveform in

Figure 4 shows the sequence of events, clocking and control signal states needed for

successful configuration in CPU mode.

Valid Bitstream Data

CPU_CLK

CONFIG_RSTN

CONFIG_STATUS

CSN

DQ[7:0]

CONFIG_DONE

1

2

3

Figure 4: Clocking and Control Signals for Successful Configuration