Achronix Speedster22i Configuration User Manual

Page 15

UG033, December 18, 2013

15

1

0

1

0

1

0

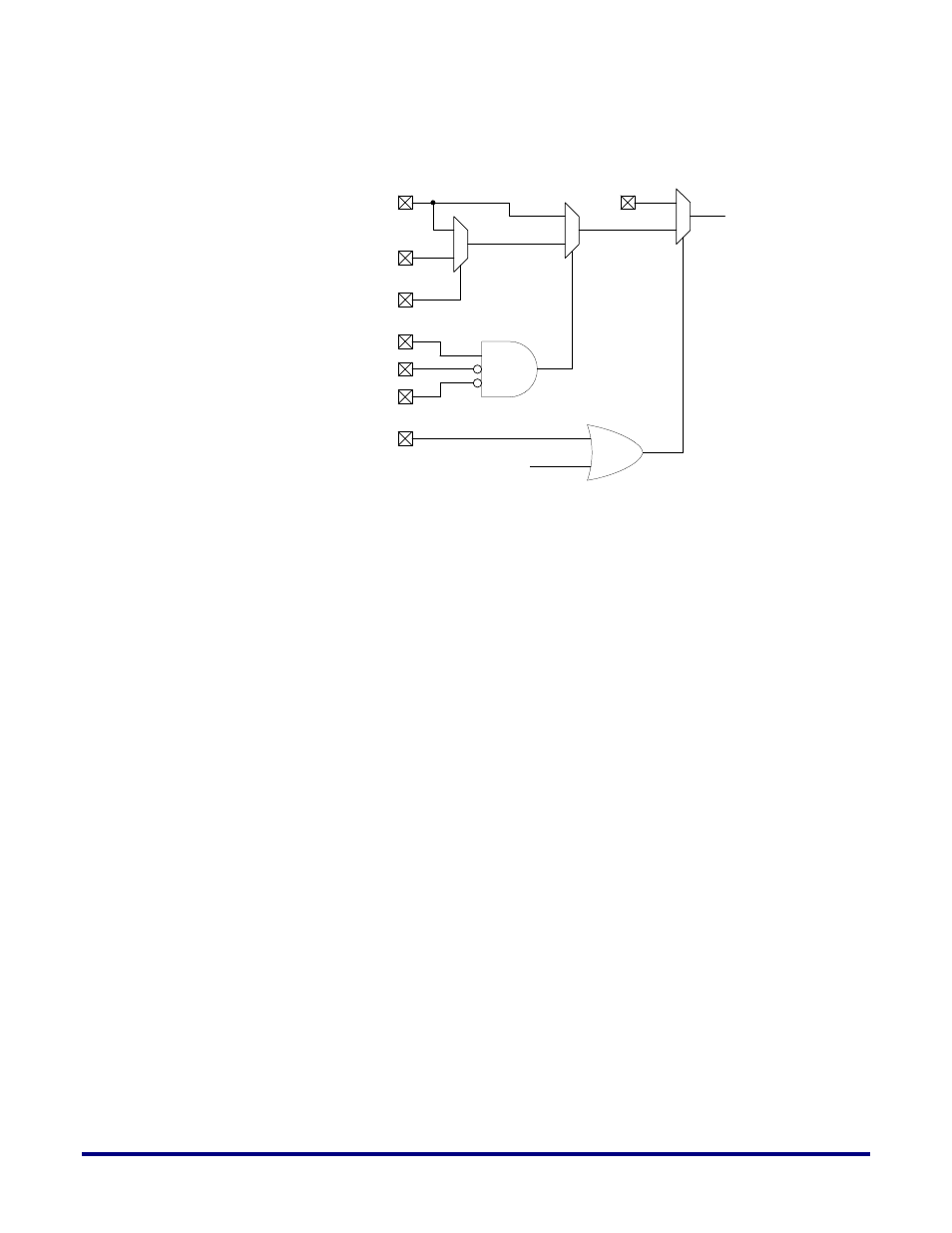

3'b100

CPU_CLK

SYSCLK

CONFIG_SYSCLK_BYPASS

TCK

CONFIG_MODESEL[2]

CONFIG_MODESEL[1]

CONFIG_MODESEL[0]

CONFIG_CLKSEL

JTAG_CLKSEL

(From Internal FCU)

FCU_CLK

Figure 10: FPGA Configuration Clock Selection Logic

Note that if programming will be done exclusively using JTAG mode, it is important to

understand how to control the CONFIG_MODESEL and clock selection pins. In order to clear

the FPGA configuration memory after a power-on or a reset of the device, an active (non-

JTAG) clock needs to be selected to cycle through the FCU states. For example, if

CONFIG_MODESEL is set to ‘100’ (thereby selecting CPU_CLK prior to the JTAG override),

CPU_CLK needs to be toggled to ensure correct operation.