Pin descriptions, Osc1; osc2 - master clock, Cs - chip select – Cirrus Logic CS5534-BS User Manual

Page 44: Clock generator

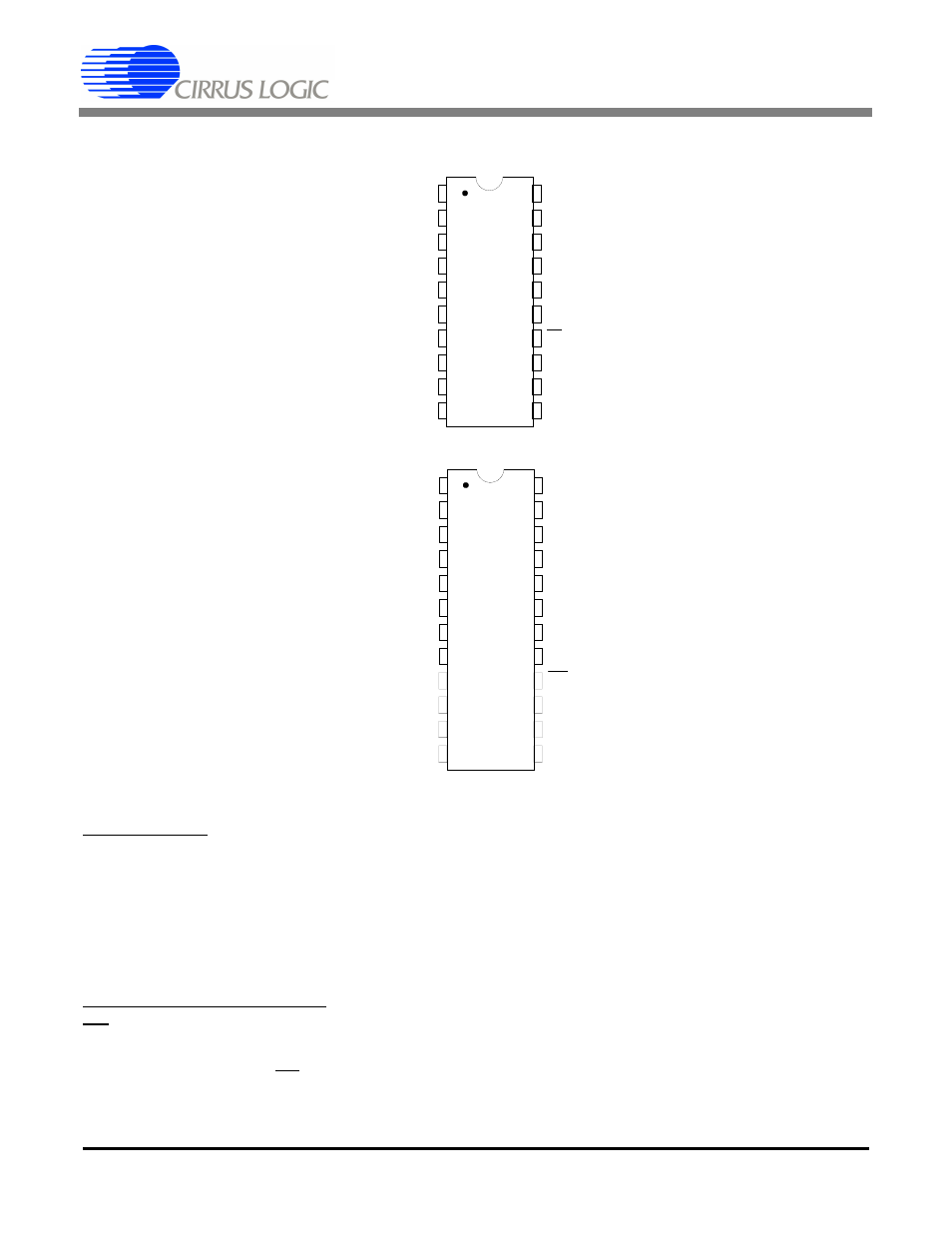

CS5532/34-BS

44

DS755F3

3. PIN DESCRIPTIONS

Clock Generator

OSC1; OSC2 - Master Clock.

An inverting amplifier inside the chip is connected between these pins and can be used with a

crystal to provide the master clock for the device. Alternatively, an external (CMOS compatible)

clock (powered relative to VD+) can be supplied into the OSC2 pin to provide the master clock

for the device.

Control Pins and Serial Data I/O

CS - Chip Select.

When active low, the port will recognize SCLK. When high the SDO pin will output a high

impedance state. CS should be changed when SCLK = 0.

1

2

3

4

5

6

7

8

13

14

15

16

17

18

19

20

VREF+

VREF-

SCLK

CS

DGND

A1

A0

VA-

VA+

C2

C1

AIN1-

AIN1+

9

10

11

12

SDO

OSC1

OSC2

SERIAL DATA INPUT

LOGIC OUTPUT (ANALOG)/GUARD

POSITIVE ANALOG POWER

AMPLIFIER CAPACITOR CONNECT

AMPLIFIER CAPACITOR CONNECT

DIFFERENTIAL ANALOG INPUT

CHIP SELECT

VOLTAGE REFERENCE INPUT

VOLTAGE REFERENCE INPUT

DIFFERENTIAL ANALOG INPUT

DIFFERENTIAL ANALOG INPUT

SERIAL CLOCK INPUT

POSITIVE DIGITAL POWER

DIGITAL GROUND

SERIAL DATA OUT

MASTER CLOCK

DIFFERENTIAL ANALOG INPUT

AIN2+

AIN2-

SDI

VD+

NEGATIVE ANALOG POWER

MASTER CLOCK

LOGIC OUTPUT (ANALOG)/GUARD

CS5532

1

2

3

4

5

6

7

8

17

18

19

20

21

22

23

24

9

10

11

12

13

14

15

16

VREF+

VREF-

CS

DGND

SDO

SERIAL DATA INPUT

POSITIVE ANALOG POWER

AMPLIFIER CAPACITOR CONNECT

AMPLIFIER CAPACITOR CONNECT

DIFFERENTIAL ANALOG INPUT

CHIP SELECT

VOLTAGE REFERENCE INPUT

VOLTAGE REFERENCE INPUT

DIFFERENTIAL ANALOG INPUT

DIFFERENTIAL ANALOG INPUT

POSITIVE DIGITAL POWER

DIGITAL GROUND

SERIAL DATA OUT

MASTER CLOCK

DIFFERENTIAL ANALOG INPUT

AIN3+

AIN3-

SDI

VD+

NEGATIVE ANALOG POWER

DIFFERENTIAL ANALOG INPUT

DIFFERENTIAL ANALOG INPUT

DIFFERENTIAL ANALOG INPUT

DIFFERENTIAL ANALOG INPUT

AIN2-

AIN2+

A1

A0

VA-

VA+

C2

C1

AIN4-

AIN4+

OSC1

OSC2

AIN1-

AIN1+

SCLK

SERIAL CLOCK INPUT

LOGIC OUTPUT (ANALOG)/GUARD

LOGIC OUTPUT (ANALOG)/GUARD

MASTER CLOCK

CS5534