No offset dac, Figure 6. cs5532/34 register diagram – Cirrus Logic CS5534-BS User Manual

Page 14

CS5532/34-BS

14

DS755F3

2.1.4. No Offset DAC

An offset DAC was not included in the CS553X

family because the high dynamic range of the con-

verter eliminates the need for one. The offset regis-

ter can be manipulated by the user to mimic the

function of a DAC if desired.

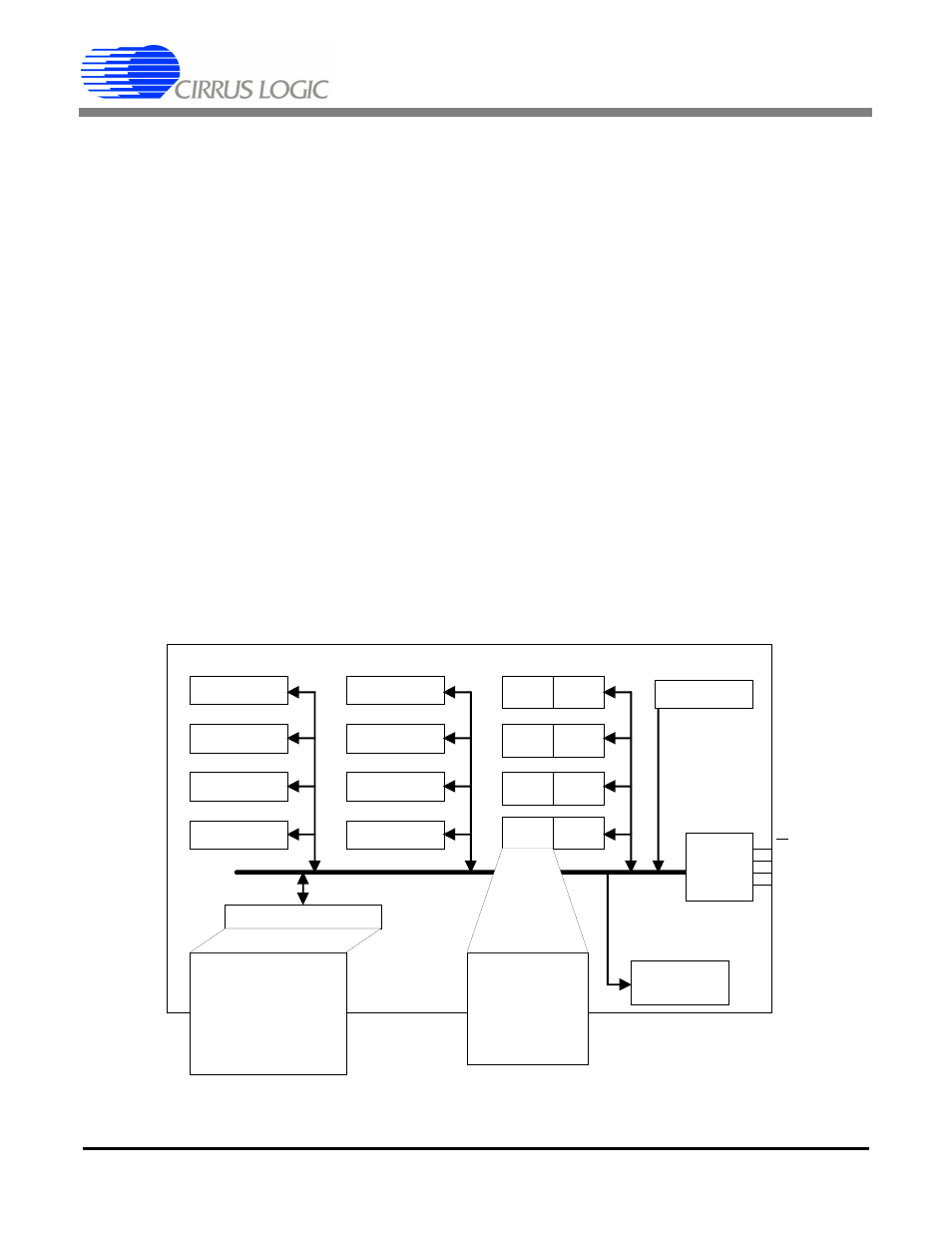

2.2. Overview of ADC Register Structure

and Operating Modes

The CS5532/34 ADCs have an on-chip controller,

which includes a number of user-accessible regis-

ters. The registers are used to hold offset and gain

calibration results, configure the chip's operating

modes, hold conversion instructions, and to store

conversion data words. Figure 6 depicts a block di-

agram of the on-chip controller’s internal registers.

Each of the converters has 32-bit registers to func-

tion as offset and gain calibration registers for each

channel. The CS5532 has two offset and two gain

calibration registers, the CS5534 has four offset

and four gain calibration registers. These registers

hold calibration results. The contents of these reg-

isters can be read or written by the user. This allows

calibration data to be off-loaded into an external

EEPROM. The user can also manipulate the con-

tents of these registers to modify the offset or the

gain slope of the converter.

The converters include a 32-bit configuration reg-

ister which is used for setting options such as the

power down modes, resetting the converter, short-

ing the analog inputs, and enabling diagnostic test

bits like the guard signal.

A group of registers, called Channel Setup Regis-

ters, are used to hold pre-loaded conversion in-

structions. Each channel setup register is 32 bits

wide, and holds two 16-bit conversion instructions

referred to as Setups. Upon power up, these regis-

ters can be initialized by the system microcontrol-

ler with conversion instructions. The user can then

instruct the converter to perform single or multiple

Offset 1 (1 x 32)

Offset 2 (1 x 32)

Offset 3 (1 x 32)

Offset 4 (1 x 32)

Gain 1 (1 x 32)

Gain 2 (1 x 32)

Gain 3 (1 x 32)

Gain 4 (1 x 32)

Setup 1

(1 x 16)

Setup 2

(1 x 16)

Setup 4

(1 x 16)

Setup 6

(1 x 16)

Setup 8

(1 x 16)

Setup 3

(1 x 16)

Setup 5

(1 x 16)

Setup 7

(1 x 16)

Offset Registers (4 x 32)

Gain Registers (4 x 32)

Channel Setup

Registers (4 x 32)

Conversion Data

Register (1 x 32)

Configuration Register (1 x 32)

Power Save Select

Reset System

Input Short

Guard Signal

Voltage Reference Select

Output Latch

Output Latch Select

Channel Select

Gain

W ord Rate

Unipolar/Bipolar

Output Latch

Delay Time

Open Circuit Detect

CS

SDI

SDO

SCLK

Read

O

n

ly

Com mand

Register (1 × 8)

Wr

it

e

O

n

ly

Serial

Interface

Data (1 x 32)

Offset/Gain Select

Filter Rate Select

Offset/Gain Pointer

Figure 6. CS5532/34 Register Diagram