Cs5484 – Cirrus Logic CS5484 User Manual

Page 42

CS5484

42

DS981F3

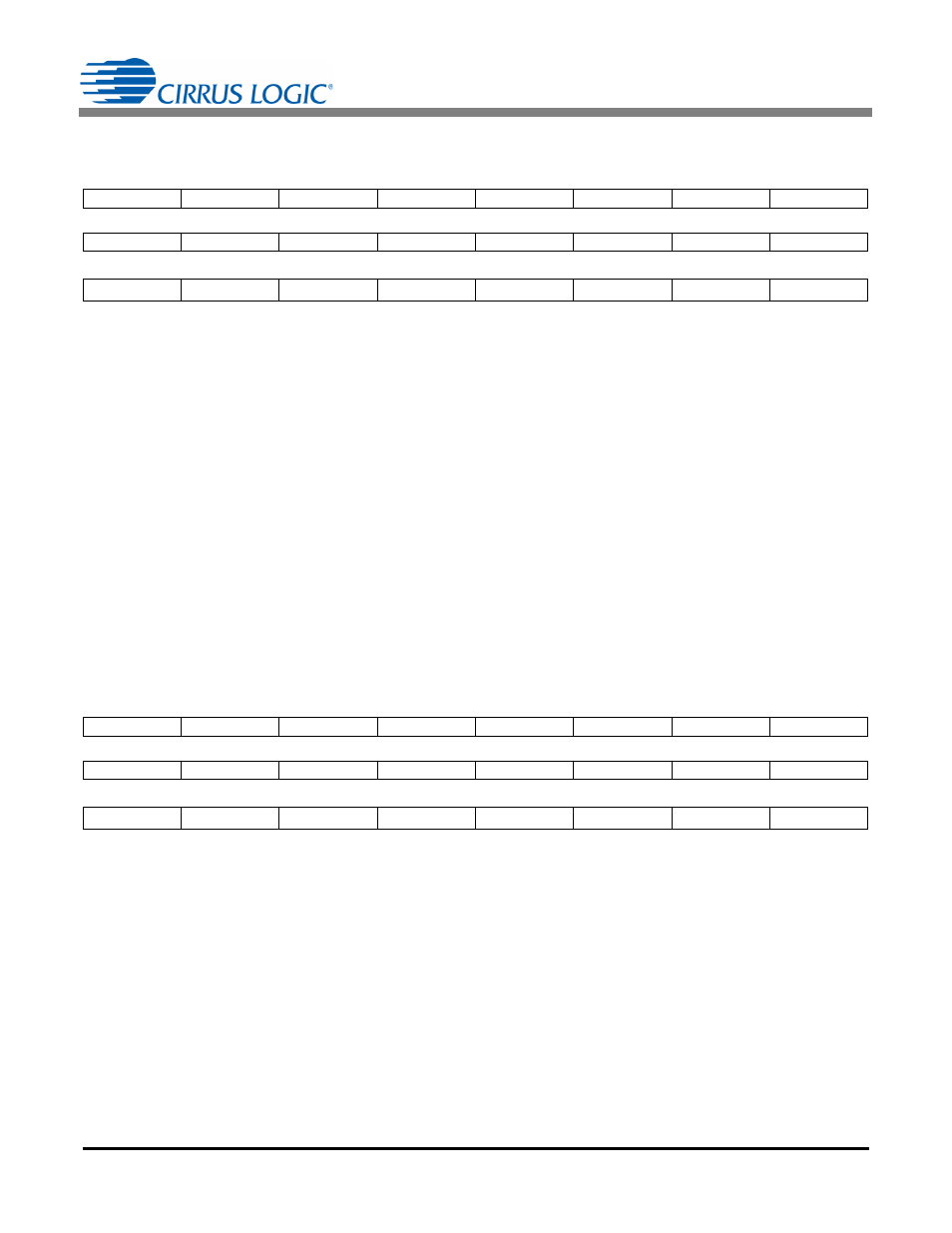

6.6.8 Pulse Output Control (PulseCtrl) – Page 0, Address 9

Default = 0x00 0000

This register controls the input to the energy pulse generation block (EPGx).

[23:16]

Reserved.

EPGxIN[3:0]

Selects the input to the energy pulse generation block (EPGx).

0000 = P1

AVG

(Default)

0001 = P2

AVG

0010 = P

SUM

0011 = Q1

AVG

0100 = Q2

AVG

0101 = Q

SUM

0110 = S1

0111 = S2

1000 = S

SUM

1001 = Unused

...

1111 = Unused

6.6.9 Register Lock Control (RegLock) – Page 0, Address 34

Default = 0x00 0000

[23:13]

Reserved.

DSP_LCK[4:0]

DSP_LCK[4:0] = 0x16 sets the DSP lockable registers to be write protected from the

CS5484 internal calculation engine. Writing 0x09 unlocks the registers.

[7:5]

Reserved.

HOST_LCK[4:0]

HOST_LCK[4:0] = 0x16 sets all the registers except RegLock, Status0, Status1, and

Status2 to be write protected from the serial interface. Writing 0x09 unlocks the regis-

ters.

23

22

21

20

19

18

17

16

-

-

-

-

-

-

-

-

15

14

13

12

11

10

9

8

EPG4IN[3]

EPG4IN[2]

EPG4IN[1]

EPG4IN[0]

EPG3IN[3]

EPG3IN[2]

EPG3IN[1]

EPG3IN[0]

7

6

5

4

3

2

1

0

EPG2IN[3]

EPG2IN[2]

EPG2IN[1]

EPG2IN[0]

EPG1IN[3]

EPG1IN[2]

EPG1IN[1]

EPG1IN[0]

23

22

21

20

19

18

17

16

-

-

-

-

-

-

-

-

15

14

13

12

11

10

9

8

-

-

-

DSP_LCK[4]

DSP_LCK[3]

DSP_LCK[2]

DSP_LCK[1]

DSP_LCK[0]

7

6

5

4

3

2

1

0

-

-

-

HOST_LCK[4] HOST_LCK[3] HOST_LCK[2] HOST_LCK[1] HOST_LCK[0]