1 i2c slave transfer formats, C slave transfer formats, Figure 4-2: i – PNI SENtral User Manual

Page 15: C slave write example, Figure 4-3: i, C slave read example, with repeated start, Figure 4-4: i, C slave write register address only, Figure 4-5: i, C slave read register from current address

PNI Sensor Corporation

Doc #1018049 R03

SENtral Technical Data Sheet

Page 14

Data transfer is always initiated by the host. Data is transferred between the host and

SENtral serially through the data line (SDAS) in an 8-bit transfer format. The transfer is

synchronized by the serial clock line, SCLS. Supported transfer formats are single-byte read,

multiple-byte read, single-byte write, and multiple-byte write. The data line can be driven

either by the host or SENtral. Normally the serial clock line will be driven by the host,

although exceptions can exist when clock-stretching is implemented in Pass-Through State.

4.2.1

I

2

C Slave Transfer formats

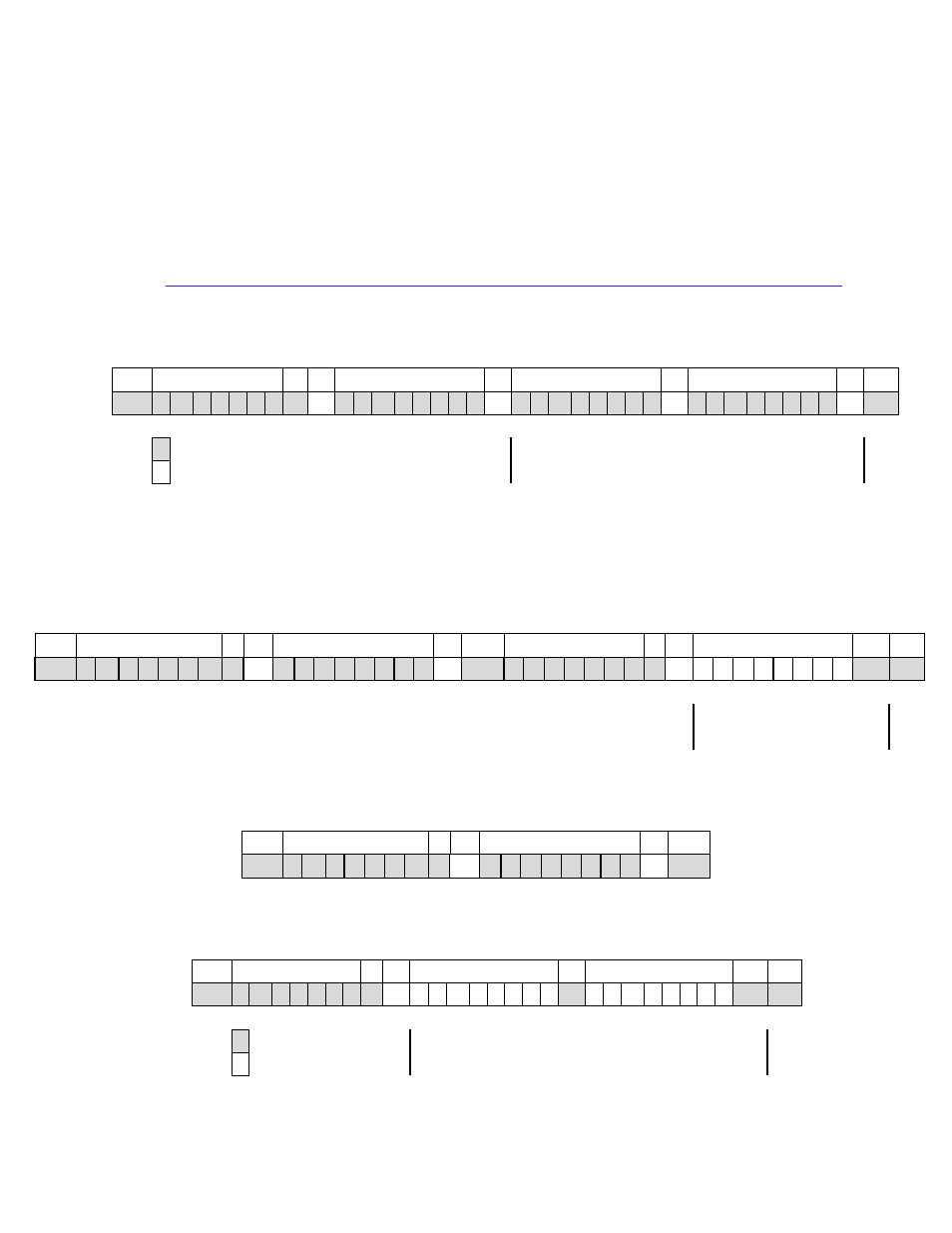

Figure 4-2 illustrates writing data to registers in single-byte or multiple-byte mode.

START

SLAVE ADDRESS

RW ACK REGISTER ADDRESS (N) ACK

DATA TO REGISTER (N)

ACK DATA TO REGISTER (N+1) ACK STOP

S

A6 A5 A4 A3 A2 A1 A0 0

0 R7 R6 R5 R4 R3 R2 R1 R0 0 D7 D6 D5 D4 D3 D2 D1 D0 0 D7 D6 D5 D4 D3 D2 D1 D0 0

P

From Host to SENtral

------------ Data Transferred (n bytes + acknowledge) ------------

From SENtral to Host

Figure 4-2: I

2

C Slave Write Example

The I

2

C host interface supports both a read sequence using repeated START conditions,

shown in Figure 4-3, and a sequence in which the register address is sent in a separate

sequence than the data, shown in Figure 4-4 and Figure 4-5.

START

SLAVE ADDRESS

RW ACK

REGISTER ADDRESS (N)

ACK START

SLAVE ADDRESS

RW ACK DATA FROM REGISTER (N) NACK STOP

S

A6 A5 A4 A3 A2 A1 A0 0

0

R7 R6 R5 R4 R3 R2 R1 R0

0

SR

A6 A5 A4 A3 A2 A1 A0 1

0

D7 D6 D5 D4 D3 D2 D1 D0

1

P

Data Transferred

(n bytes + acknowledge)

Figure 4-3: I

2

C Slave Read Example, with Repeated START

START

SLAVE ADDRESS

RW ACK

REGISTER ADDRESS (N)

ACK STOP

S

A6 A5 A4 A3 A2 A1 A0 0

0

R7 R6 R5 R4 R3 R2 R1 R0

0

P

Figure 4-4: I

2

C Slave Write Register Address Only

START

SLAVE ADDRESS

RW ACK

DATA FROM REG. (N)

ACK

DATA FROM REG. (N+1)

NACK STOP

S

A6 A5 A4 A3 A2 A1 A0 1

0 D7 D6 D5 D4 D3 D2 D1 D0 0 D7 D6 D5 D4 D3 D2 D1 D0

1

P

From Host to SENtral

-------------- Data Transferred (n bytes + acknowledge) --------------

From SENtral to Host

Figure 4-5: I

2

C Slave read register from current address