4 i2c interface, 1 i2c timing, C interface – PNI SENtral User Manual

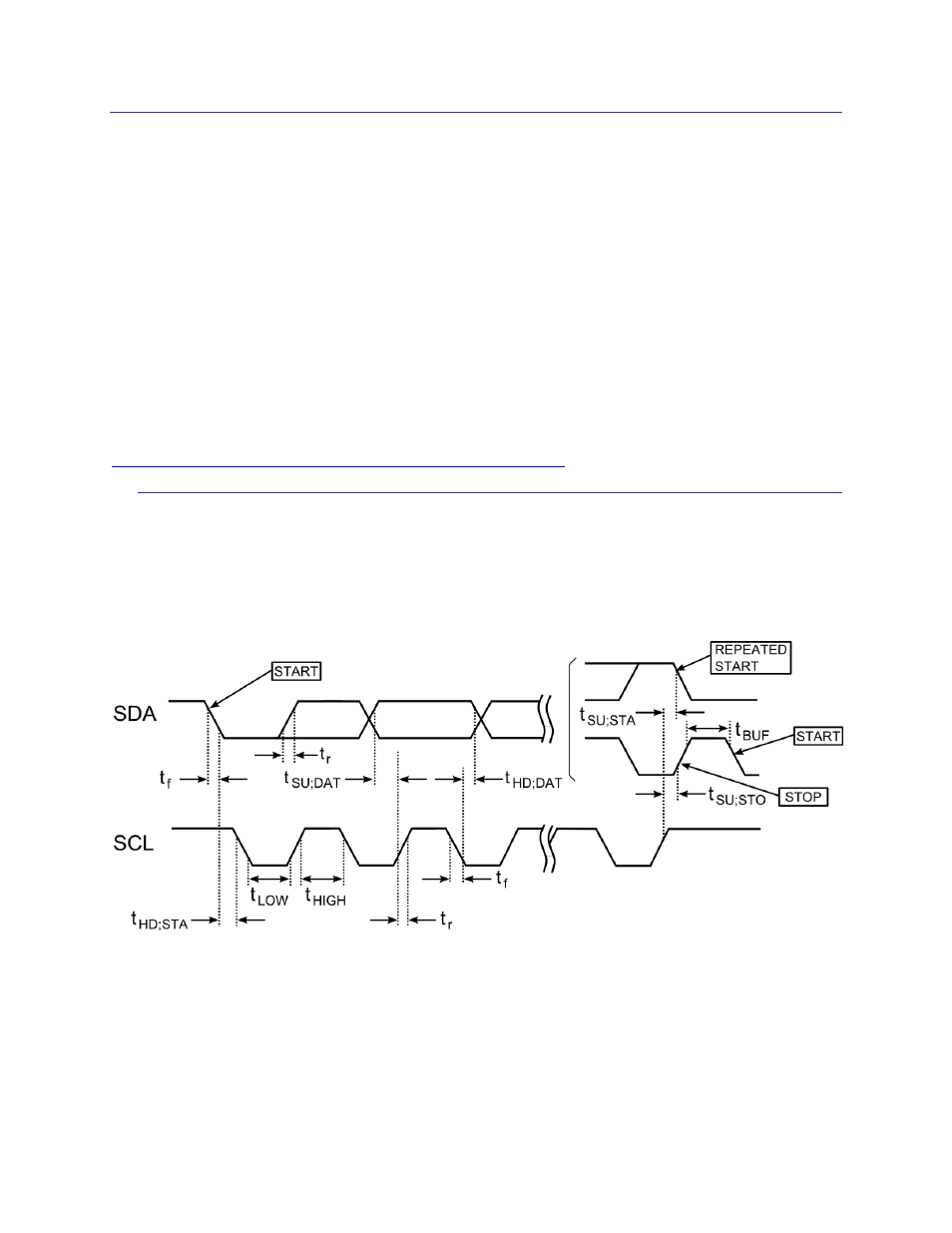

Page 13: C timing, Figure 4-1: i, C timing diagram

PNI Sensor Corporation

Doc #1018049 R03

SENtral Technical Data Sheet

Page 12

4

I

2

C Interface

Communication with the host processor and sensors is via an I

2

C interface and interrupt lines.

The SENtral Motion Coprocessor acts as the I

2

C master with the sensors and as a slave with the

host processor. The sensor interrupt lines let SENtral know when new data is available, while

the host interrupt line lets the host system know when SENtral has updated the quaternions. The

sensor and host output data rates are set by the MagRate, AccelRate, GyroRate, and

QRateDivisor registers.

SENtral’s I

2

C interface complies with NXP’s UM10204 specification and user manual, rev 04.

Standard, Fast, Fast Plus, and High Speed modes of the I

2

C protocol are supported by SENtral’s

I

2

C host interface. Below is a link to this document.

4.1 I

2

C Timing

SENtral’s I

2

C timing requirements are set forth below, in Figure 4-1 and Table 4-1. For the

timing requirements shown in Figure 4-1, transitions are 30% and 70% of V

DD

.

Figure 4-1: I

2

C Timing Diagram