KB Electronics KBAC-48 User Manual

Page 21

21

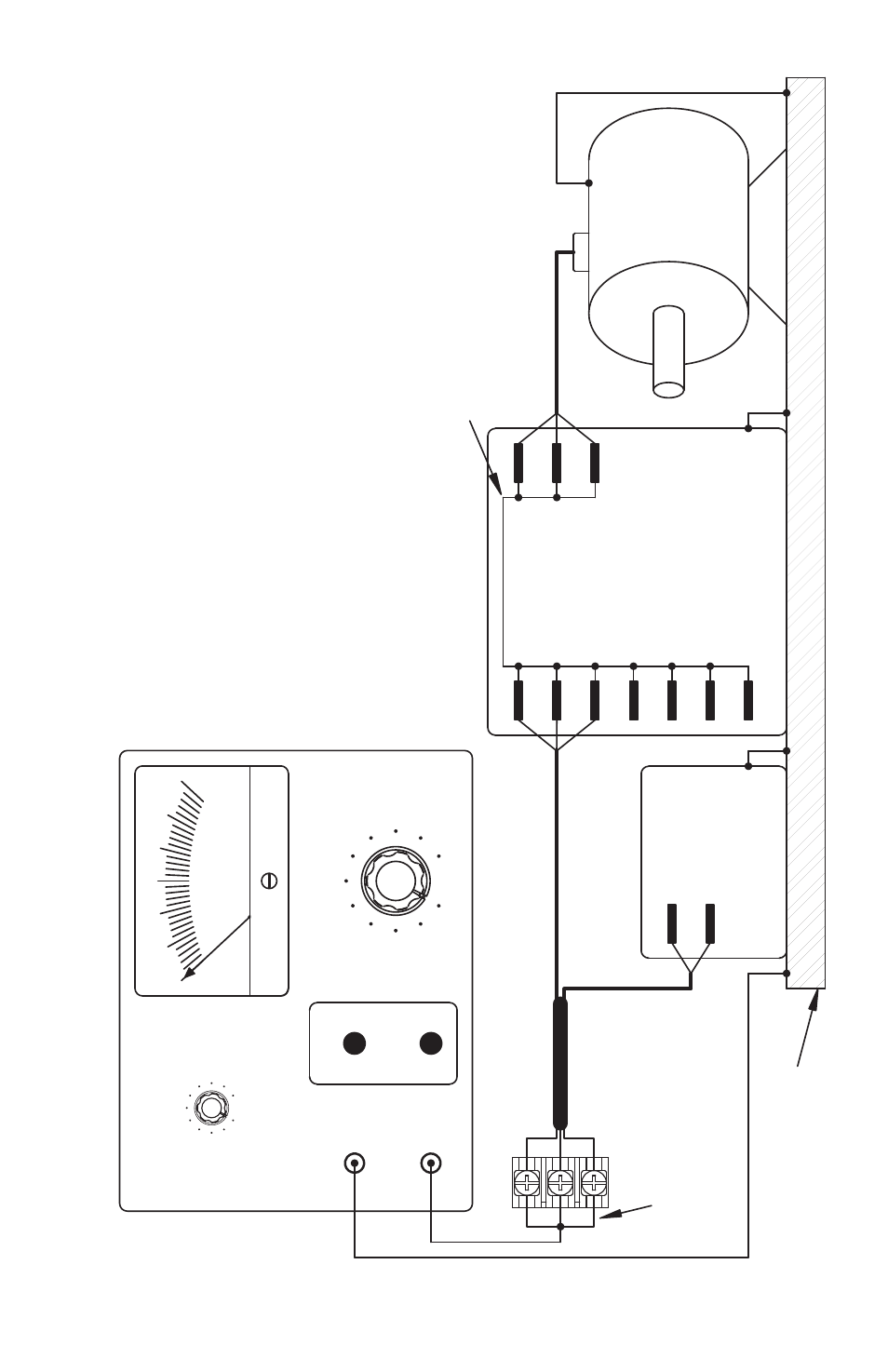

Chassis

P3

Chassis

Machine E

quipmen

t or F

rame

Adjustable F

requenc

y D

rive

(Main P

ow

er D

isconnec

ted)

to A

C Line Inputs

Connec

t Hi-P

ot

L2

L1

P2

P1

Auxiliar

y E

quipmen

t

L3

Signal Inputs

L2

H. V

.

AC Line Input

MAX

ZERO

L1

RESET

RETURN

10mA

0mA

VOL

TA

GE

TEST

AC KIL

OV

OL

TS

LEAK

AGE

1

0

3

2

High V

oltage

Dielec

tric W

ithstand T

est

er (Hi-P

ot T

est

er)

Mot

or W

ires

W

V

Frame

Connec

t A

ll D

rive T

erminals T

ogether

U

(Main P

ow

er D

isconnec

ted)

Figur

e 29 –

Typic

al Hi-P

ot

Test S

etup