Rainbow Electronics BR24C21FV User Manual

Page 9

BR24C21 / BR24C21F / BR24C21FJ / BR24C21FV

Memory ICs

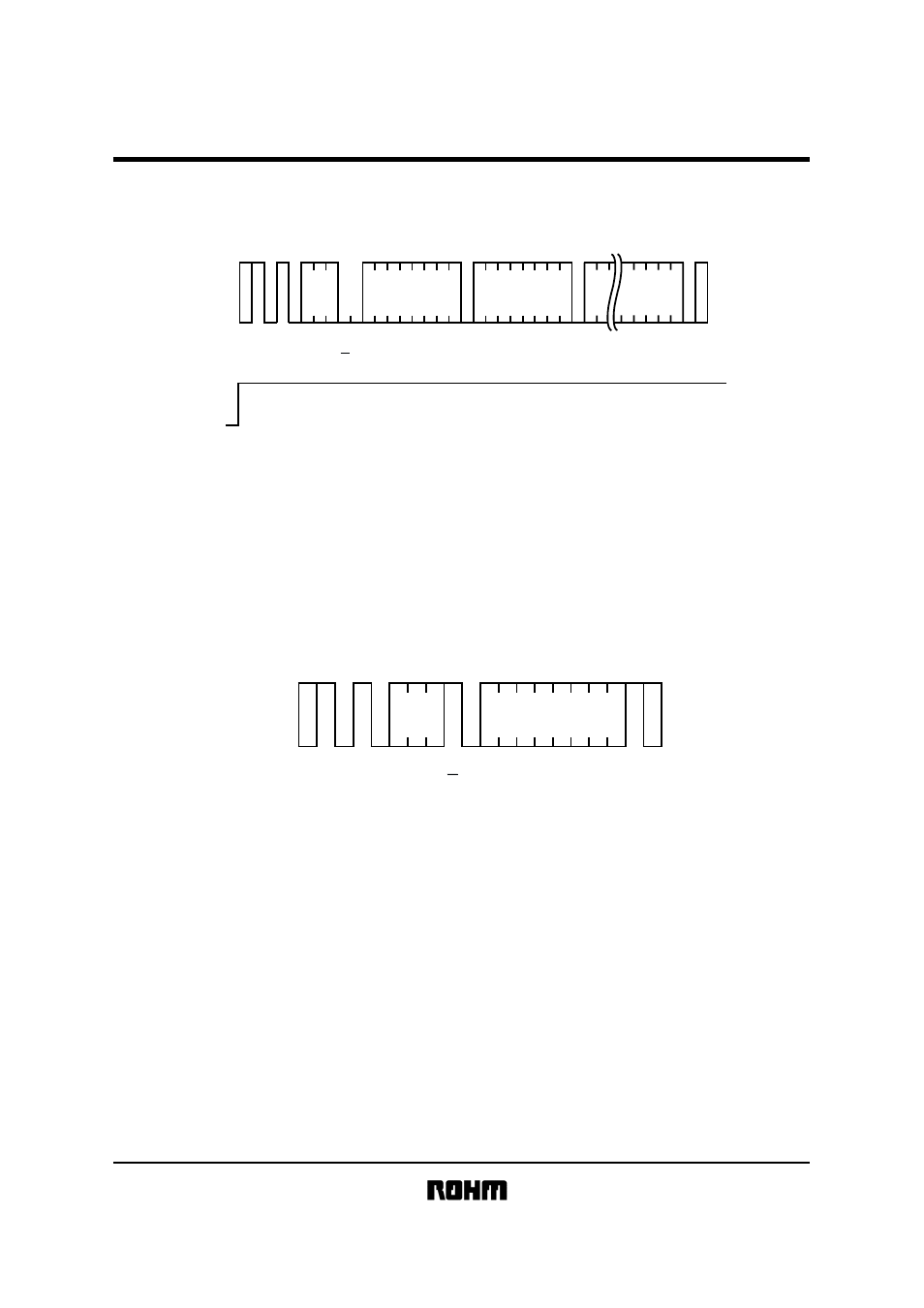

PAGE WRITE

SDA

LINE

VCLK

S

T

A

R

T

SLAVE

ADDRESS

1 0

0

1

∗ ∗ ∗

A

C

K

R

/

W

W

R

I

T

E

WORD

ADDRESS(n)

D7

DATA(n)

D0

A

C

K

Fig.16 PAGE WRITE CYCLE TIMING

WA

0

WA

6

∗

DATA(n

+

7)

D0

A

C

K

S

T

O

P

A

C

K

∗

Don't care

•If the master transmits the next data instead of generating a stop condition in byte write cycle, the BR24C21,

BR24C21F, BR24C21FJ and BR24C21FV transfer from byte write cycle to page write cycle. After the receipt of each

word, the three lower order address pointer bits are internally incremented by one. The high order five bits of the word

address remains constant.

If the master transmits more than eight words, prior to generating the STOP condition, the address counter will “roll

over”, and the previous transmitted data will be overwritten.

CURRENT READ

SDA

LINE

S

T

A

R

T

SLAVE

ADDRESS

1

1

R

/

W

A

C

K

A

C

K

DATA

S

T

O

P

0

0

∗

∗ ∗

D7

D0

R

E

A

D

Fig.17 CURRENT READ CYCLE TIMING

•The BR24C21, BR24C21F, BR24C21FJ and BR24C21FV contain an internal address counter which maintains the

address of the last word accessed, incremented by one. If the last accessed address is address n in a read operation,

the next read operation will access data from address n+1 and increment the current address counter. If the last

accessed address is address n in a write operation, the next read operation will access data from address n. If the

master does not transfer the acknowledge but does generate a stop condition, the current address read operation

only provides a single byte of data. At this point, the device discontinues transmission.