Rainbow Electronics BR24C21FV User Manual

Page 8

BR24C21 / BR24C21F / BR24C21FJ / BR24C21FV

Memory ICs

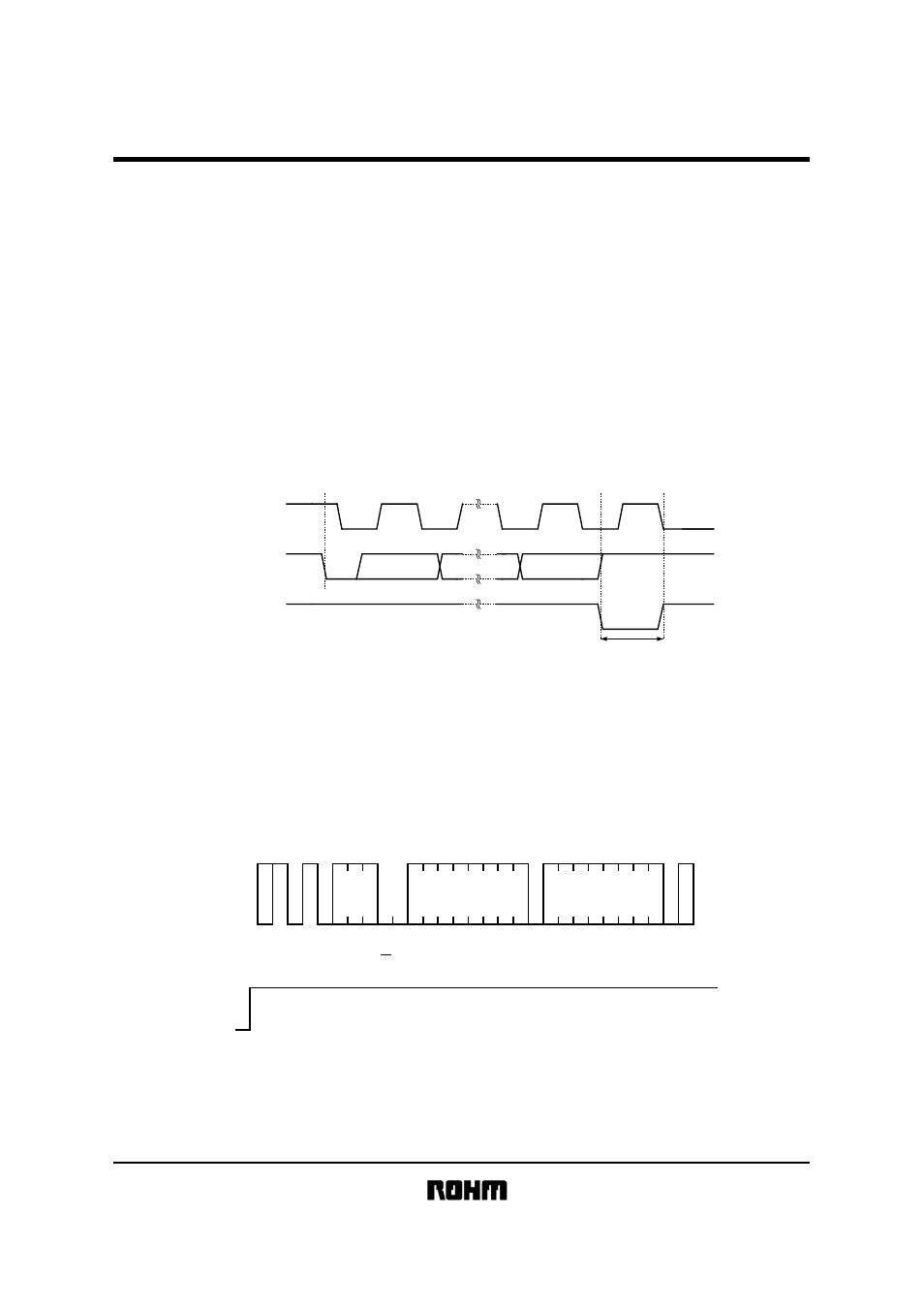

ACKNOWLEDGE

•Acknowledge is a software convention used to indicate successful data transfers. The master or the slave will release

the bus after transmitting eight bits. During the ninth clock cycle, the receiver will pull the SDA line LOW to

acknowledge that the eight bits of data has been received.

•The BR24C21, BR24C21F, BR24C21FJ and BR24C21FV will respond with an Acknowledge after recognition of a

START condition and its slave address. If both the device and a write operation have been selected, the BR24C21,

BR24C21F, BR24C21FJ and BR24C21FV will respond with an Acknowledge, after the receipt of each subsequent

8-bit word.

•In the READ mode, the BR24C21, BR24C21F, BR24C21FJ and BR24C21FV will transmit eight bits of data, release

the SDA line, and monitor the line for an Acknowledge.

•If an Acknowledge is detected, and no STOP condition is generated by the master, the BR24C21, BR24C21F,

BR24C21FJ, BR24C21FV will continue to transmit the data.

•If an Acknowledge is not detected, the BR24C21, BR24C21F, BR24C21FJ and BR24C21FV will terminate further

data transmissions and await a STOP condition before returning to the standby mode.

1

8

9

SCL

SDA

SDA

START CONDITION

(START BIT)

Acknowledge Signal

(ACK Signal)

(From

µ−

COM)

OUTPUT DATA)

(

µ−

COM

(IC OUTPUT DATA)

Fig.14 ACKNOWLEDGE RESPONSE FROM RECEIVER

3) Bi-directional Mode Command

BYTE WRITE

SDA

LINE

VCLK

S

T

A

R

T

SLAVE

ADDRESS

1 0

0

1

R

/

W

W

R

I

T

E

D7

DATA

D0

A

C

K

S

T

O

P

Fig.15 BYTE WRITE CYCLE TIMING

A

C

K

WORD

ADDRESS

A

C

K

WA

0

WA

6

∗

Don't care

∗

∗

∗

∗

•When the master generates a STOP condition, the BR24C21, BR24C21F, BR24C21FJ and BR24C21FV begin the

internal write cycle to the nonvolatile array.