Rainbow Electronics AT45DB161E User Manual

Page 71

71

Adesto AT45DB161E [DATASHEET]

8782D–DFLASH–11/2012

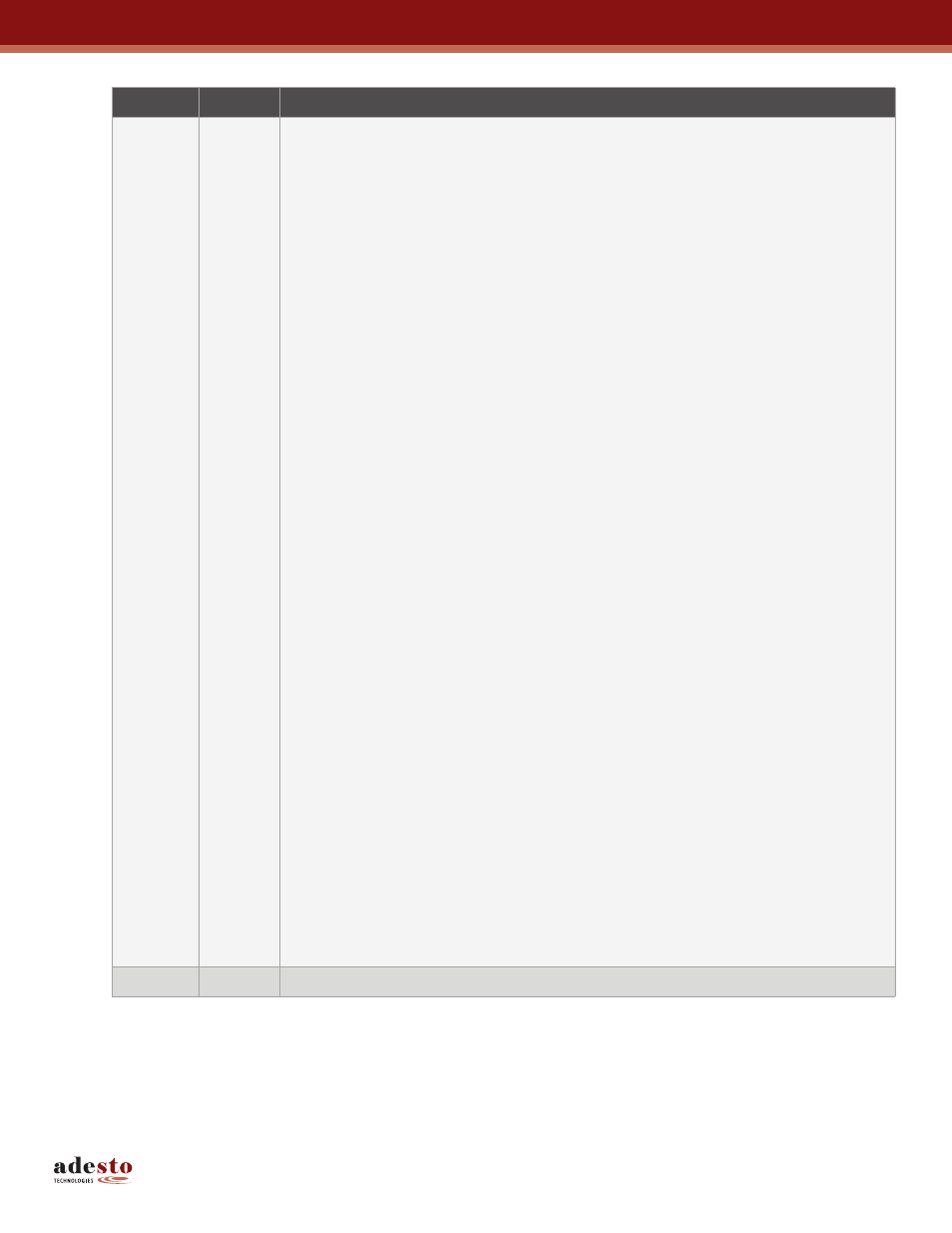

8782B

06/2012

Update “Enable Sector Protection”, “Disable Sector Protection”, “Erase Sector Protection

Register”, “Program Sector Protection Register”, and “Read Sector Lockdown Register” figures.

Correct descriptions for PAGE SIZE, bit 0 in “Status Register Format – Byte 1” table.

Insert 1Bh opcode in “Detailed Bit-level Addressing Sequence for Binary Page Size (512 bytes)”

and “Detailed Bit-level Addressing Sequence for Standard DataFlash Page Size

(528 bytes)” tables.

DC Characterisitcs:

Add I

CC1

condition of f = 20MHz; I

OUT

= 0mA; V

CC

= 3.6V with typical 7.5mA and

maximum 10mA.

Add I

CC4

– Active Current, Erase Operation, V

CC

= 3.6V, typical 14mA and maximum 20mA.

Update I

ZP

to I

UDPD

– decrease typical from 0.5μA to 0.4μA and maximum from 2μA to 1μA.

Update I

DP

to I

DPD

and I

SP

to I

SB

.

Update I

CC0

to I

CC1

– decrease typical 7mA to 6.5mA.

Update I

CC1

to I

CC2

– 33MHZ, increase maximum from 17mA to 19mA;

50MHz, decrease maximum from 20mA to 19mA; and at

85MHz, increase typical 14mA to 16mA and maximum 23mA to 26mA.

Update I

CC2

to I

CC3

– remove erase operation, decrease typical from 15mA to 12mA and

maximum from 20mA to 18mA.

AC Characterisitics:

Remove typical columns, t

SECP

, and t

SECUP

.

f

CAR3

– increase 2.3V/2.5V maximum 10MHz to 20MHz.

t

WH

– decrease 2.3V minimum from 6.8ns to 6.4ns and 2.5V minimum from 6.8ns to 5.2ns.

t

WL

– decrease 2.3V minimum from 6.8ns to 6.4ns and 2.5V minimum from 6.8ns to 5.2ns.

t

CS

– decrease 2.3V/2.5V minimum from 50ns to 30ns.

t

H

– decrease 2.3V/2.5V minimum from 3ns to 1ns.

t

DIS

– decrease 2.3V maximum from 35ns to 7ns and 2.5V from 35ns to 6ns.

t

V

– decrease 2.3V maximum from 8ns to 7ns.

t

COMP

– decrease 2.3V/2.5V maximum from 250μs to 220μs.

Program and Erase Characteristics:

Remove 2.3V minimum, typical, and maximum columns.

t

EP

– decrease typical from 17ms to 15ms and maximum from 50ms to 40ms.

t

PE

– decrease typical from 15ms to 12ms and maximum from 50ms to 35ms.

t

SE

– decrease typical from 1.6s to 1.4s and maximum from 5s to 3.5s.

t

CE

– decrease typical from 25s to 22s and maximum from 60s to 40s.

Update ordering code detail.

Replace package option from 9C1-CBGA to 9CC1-UBGA.

Various topographical edits throughout document.

Update template.

8782A

03/2012

Initial document release.

Doc. Rev.

Date

Comments