Using the dual adc with and asic/fpga load – Rainbow Electronics AT84AD004 User Manual

Page 52

52

AT84AD004

5390A–BDC–06/04

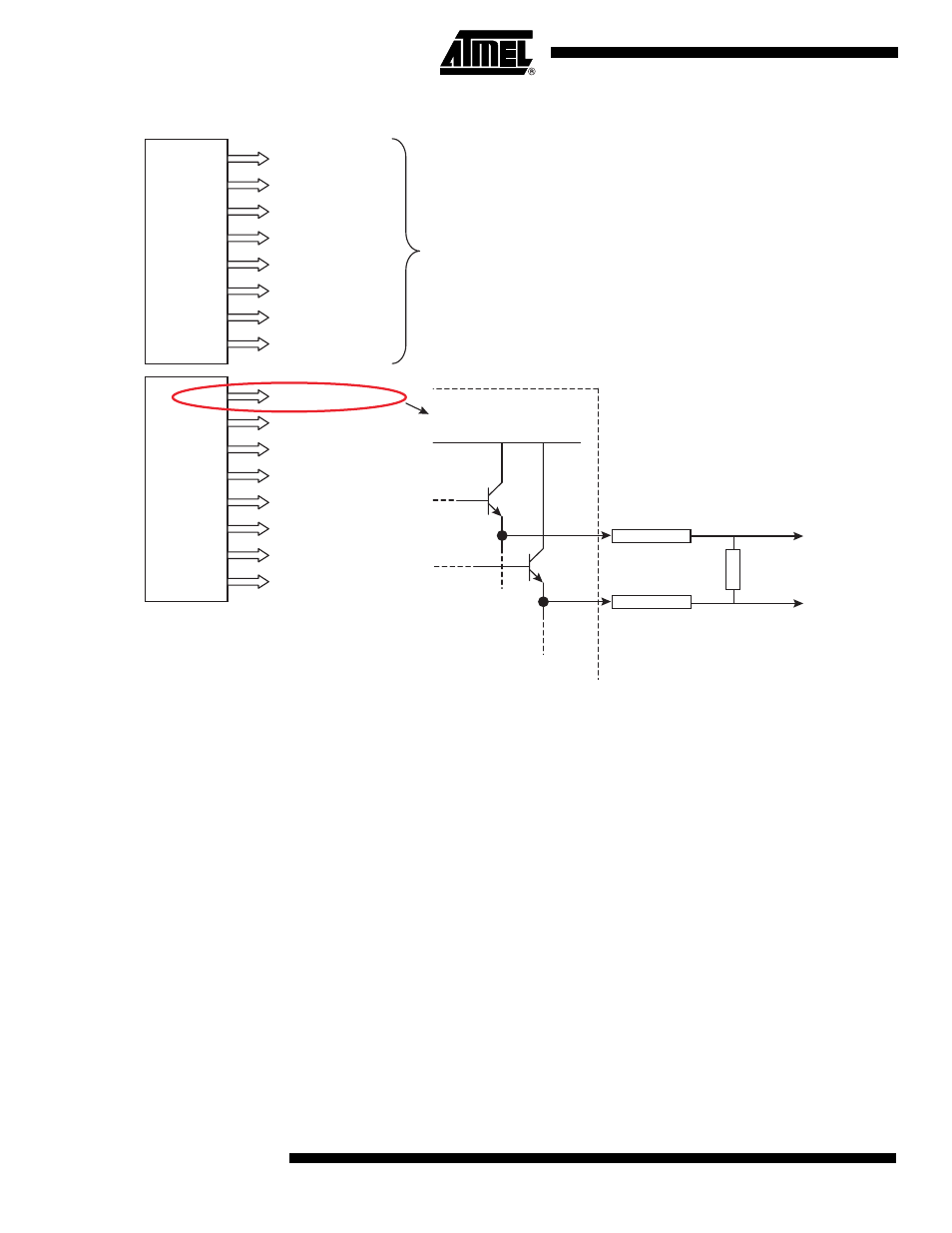

Figure 55. Example of Termination for Channel I Used in DMUX 1:1 Ratio (Port B Unused)

Note:

If the outputs are to be used in single-ended mode, it is recommended that the true and false signals be terminated with a 50

Ω

resistor.

Using the Dual ADC With

and ASIC/FPGA Load

Figure 56 on page 53 illustrates the configuration of the dual ADC (1:2 DMUX mode,

independent I and Q clocks) driving an LVDS system (ASIC/FPGA) with potential addi-

tional DMUXes used to halve the speed of the dual ADC outputs.

Port B

DOBI0 / DOBI0N

DOBI1 / DOBI1N

DOBI2 / DOBI2N

DOBI3 / DOBI3N

DOBI4 / DOBI4N

DOBI5 / DOBI5N

DOBI6 / DOBI6N

DOBI7 / DOBI7N

Floating (High Z)

Port A

DOAI0 / DOAI0N

DOAI1 / DOAI1N

DOAI2 / DOAI2N

DOAI3 / DOAI3N

DOAI4 / DOAI4N

DOAI5 / DOAI5N

DOAI6 / DOAI6N

DOAI7 / DOAI7N

VCCO

DOAI0

DOAI0N

Z0 = 50

Ω

Z0 = 50

Ω

100

Ω

LVDS In

LVDS In

Dual ADC Package

- MAX14514 (14 pages)

- MAX16825 (15 pages)

- MAX16800 (9 pages)

- MAX6931 (14 pages)

- MAX6920 (10 pages)

- MAX6959 (19 pages)

- MAX15025 (16 pages)

- EVK2 (2 pages)

- MAX13256 (17 pages)

- MAX6964 (23 pages)

- MAX6948B (28 pages)

- MAX17117 (22 pages)

- MAX6934 (16 pages)

- MAX5048 (9 pages)

- MAX15054 (9 pages)

- AT6010LV (28 pages)

- AT83C24NDS (42 pages)

- AT83C21GC (6 pages)

- AT42QT1012 (6 pages)

- ATF16LV8C (11 pages)

- ATA6823 (28 pages)

- 71M6542G (165 pages)

- ATV2500BQL (21 pages)

- ATV750BL (19 pages)

- ATA6839 (17 pages)

- BA6229 (3 pages)

- ATF16V8C (18 pages)

- ATMOS™ 1M60 (26 pages)

- ATF1504ASVL (29 pages)

- BA6955N (9 pages)

- ATF1500ABV (15 pages)

- BA6219BFP-Y (7 pages)

- AT77C102B (19 pages)

- AT90SCR050 (4 pages)

- BA6208F (2 pages)

- ATA6625 (22 pages)

- ATA6664 (20 pages)

- ATF1516ASL (13 pages)

- ATF20V8BQL (18 pages)

- ATA6827 (15 pages)

- AT83C26 (77 pages)

- AT77C104B (36 pages)

- ATA6830 (23 pages)

- AT42QT1040 (18 pages)

- ATA6824 (22 pages)